Hi, first post on here. Got wind of this place existing from marcos' VESC variant being featured on Hackaday.

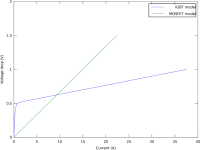

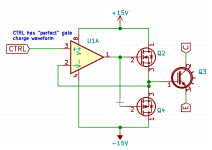

Anyway, a thought struck me the other day: IGBTs are good for higher currents due to their limited voltage drop. But there is also an almost constant bias to this drop, which is a disadvantage at lower currents. MOSFETs have the opposite properties - almost entirely linear I/V curve when fully saturated but higher voltage drop than similarly priced IGBTs at higher currents. So a thought occurs: why not parallel them? Both are driven the same way, typically have similar gate capacitances and voltages etc.

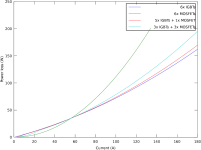

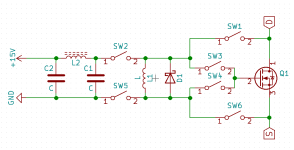

I decided to whip up a quick thing in Octave using numbers that fit two simplistic models to numbers in the datasheets for IXXX110N65B4H1 (used in the IGBT_board.pro KiCAD project) and IXFX100N65X2 (reasonably priced, low Rds(on), Vds >= 650V). Idea is we can populate a PCB like IGBT_board with six devices. How does the total power loss vs current vary with how many MOSFETs vs IGBTs we have? See attached figures.

As you might expect, one trades efficiency at higher current draws for efficiency at lower draws. Unless you just keep adding devices of course, and then it's just a question of BOM costs

Anyway, a thought struck me the other day: IGBTs are good for higher currents due to their limited voltage drop. But there is also an almost constant bias to this drop, which is a disadvantage at lower currents. MOSFETs have the opposite properties - almost entirely linear I/V curve when fully saturated but higher voltage drop than similarly priced IGBTs at higher currents. So a thought occurs: why not parallel them? Both are driven the same way, typically have similar gate capacitances and voltages etc.

I decided to whip up a quick thing in Octave using numbers that fit two simplistic models to numbers in the datasheets for IXXX110N65B4H1 (used in the IGBT_board.pro KiCAD project) and IXFX100N65X2 (reasonably priced, low Rds(on), Vds >= 650V). Idea is we can populate a PCB like IGBT_board with six devices. How does the total power loss vs current vary with how many MOSFETs vs IGBTs we have? See attached figures.

As you might expect, one trades efficiency at higher current draws for efficiency at lower draws. Unless you just keep adding devices of course, and then it's just a question of BOM costs