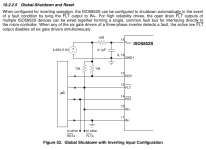

I've been thinking about adding a way to control the overshoot, by changing the negative gate control voltage, which originally was fixed at -8V.

I saw this mechanism in a tesla patent, and seemed like a fairly doable way to get control over the overshoot and switching losses. So at low phase currents we can drive the gate very hard with less switching losses, and at higher currents we can drive it softer to avoid DC bus overshoots.

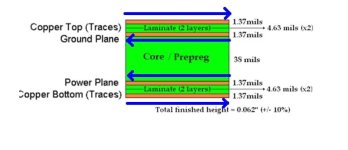

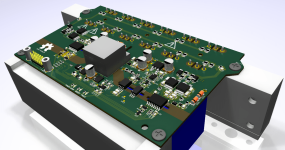

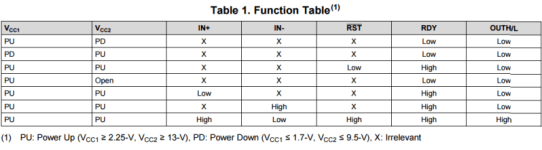

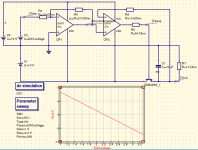

The control should come from the controller (duh) across the isolation as a variable frequency, then converted to a voltage, then used to control a voltage regulator. I've been suggested to pay close attention to the gate resistors, but those -8v were unregulated, and that can throw away all that effort. So, regulator it is.

Something not trivial in that chain is the frequency to voltage converter. There is a chip that does that with a very high linearity, but ultimately it relies on an RC circuit, and I don't like at all capacitor tolerances. IMO a better way is to put a small MCU to read the frequency and use its DAC to control the voltage.

And if I put an MCU, I get an ADC for free, so I can read voltages like Vgate, Vce, and power supplies. And there is the internal temperature sensor for free. All this is of limited use, with the ADC I can measure only every 150nsec, no chance to see high freq stuff, and its impossible to transmit such information over the isolation. But it could be useful to have an idea of the amount of overshoot and send it back to the controller. Oh, internal sensors are crap, but hey, its free.

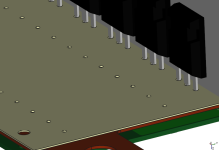

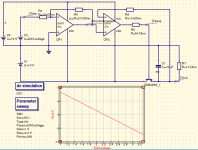

I'll keep thinking, I chose a 5x5mm MCU I'm familiar with, an isolator, and roughly simulated the voltage control.

Maybe I'll only use the ADC for Vce (its just connecting the MCU to the copper sheets below). Measuring Vgate would be interesting, but I'm adding an antenna to a critical track. Also, its not a rad hard mcu, so I don'w want to mess around with many tracks. Keep it simple, just digital in, digital out, DAC and 1 analog in easy to route. I'm a bit worried about the noise immunity of those opamps though.