Hey mystamo,

I haven't made this current design open source. I'm not sure if I'm going to take this down that road or not. It might be worth while to get more people interested in my higher power designs I have in progress (+1000A).

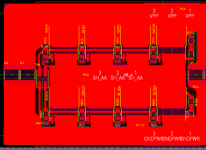

My VESC controller is similar to the Axiom schematic, but I've modified it quite a bit to suit my own needs and reduce cost. There isn't anything unique about it's design, it's just several standard practices combined. I did not isolate my phase and DC bus voltage measurements with ISOamps like Axiom did because everything is running through voltage dividers. The chance of high voltage making it across the divider is pretty small, at 200V there is only 5mA available after the first part of the voltage divider which consists of three 13k resistors in series. If the low side resistor were to fail, then it's possible this 200V @ 5mA could find it's way onto the controller, where it runs into a op amp which is used to convert the 0-5V signal into a 0-3.3V signal for the Adc input of the processor. The risk for injury is low. Lethal current starts > 100mA from everything I've read so far. An end user would also have to complete the circuit to ground while touching the high votlage.

All other signals from the power stage are isolated, current sensors and gate driver which includes fault detection and PWM.

All voltage and current signals are fed into an active Butterworth low pass filter for noise reduction. I decided to keep all my sensor interfaces at 5V vs 3.3V to increase the signal to noise ratio. All the digital inputs to the processor are processed through by directional 5V-3.3V converters.

As for getting the VESC to run, I had to build out a Linux environment for compiling the firmware and verify I could successfully build the stock VESC firmware on GIT. After that it was a matter of plodding through the .h and .c files in the hwconf directory. I made several side by side comparisons with the Axiom conf files as they are using external sensors. It was a matter of hacking and slashing my way through the code for about 3 days, then finding several errors I had made in wiring up my controller. Messing up wiring on the first go is almost a given, it was just minor stuff like swapping phase A and C signals. Because I have hardware fault detection I wasn't overly concerned about causing damage. The error codes on my LED readout really clued me into what my issues where, I was getting shoot through, but it doesn't damage anything as the current is shut down by the gate drive in about 5us.

I'll need to do a 2nd revision of my controller boards to fix the minor errors it has, but I'm contemplating offering up this as a VESC controller to the community as a finished product which is independent of the power stage with an public schematic so end users can tweak options like filter frequency.

I'm going to be looking for others to test out a complete controller, but I'll probably need some commitments from interested parties before going into production. The power stage will be enclosed in a 3D printed case for protection, and I'm contemplating adding forced air cooling to the MOSFETs and PCBs to further increase the potential for abusive power levels.

I've added the shunts to my current sensors and they now read to 400A, however I'm unable to get over 220A because my DC bus voltage drops. This is probably a limitation of my 30V 100A power supply and it's long power leads. I'm planning to build a battery pack for more testing. I think I have 30 5Ah 6s LiPo packs. They are old and have double the internal resistance vs when they were new, but they appear to still hold a charge well enough. I just need to plan it out so it's safe to use, last thing I want is a battery fire.

I'm going to get some video of the controller pushing ~200A and time how long it takes to get to 80C on the PCB and MOSFETs