Alan B

100 GW

Progress with DipTrace

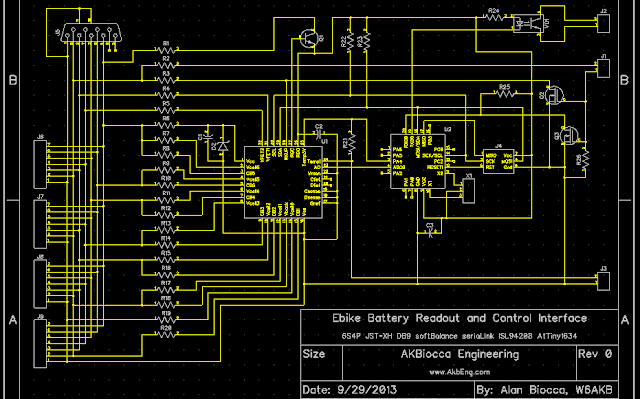

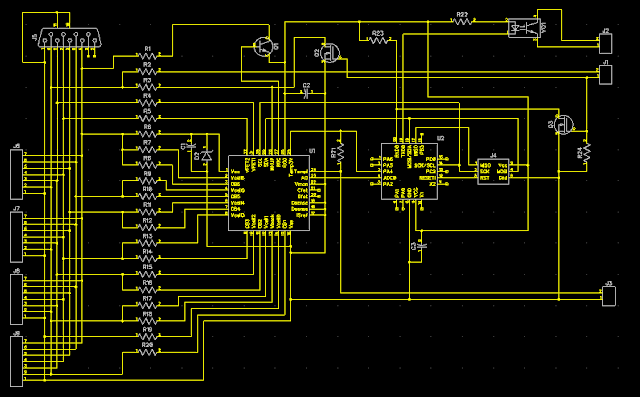

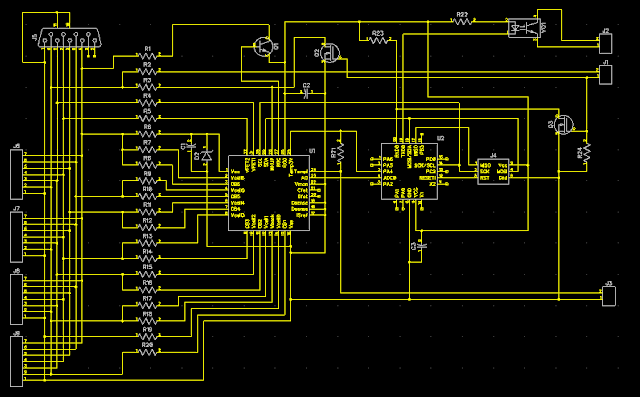

The pc board layout is pretty near complete, but I need to "do it right" and enter a schematic. So I started that yesterday.

I've just about finished the schematic already. It went pretty fast, though there are still incomplete items like some of the pad layouts. The library has a lot of parts, but often not the ones I need. DipTrace has very good tools for making parts so it doesn't take long to make or adapt one for what is needed. I haven't read the documentation, but occasionally a Google search is useful to answer a question.

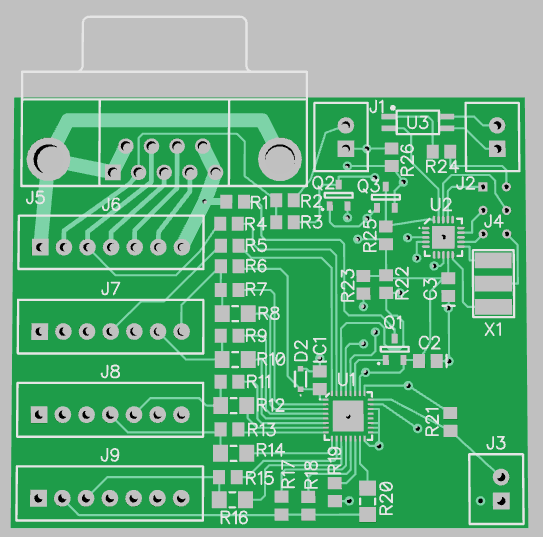

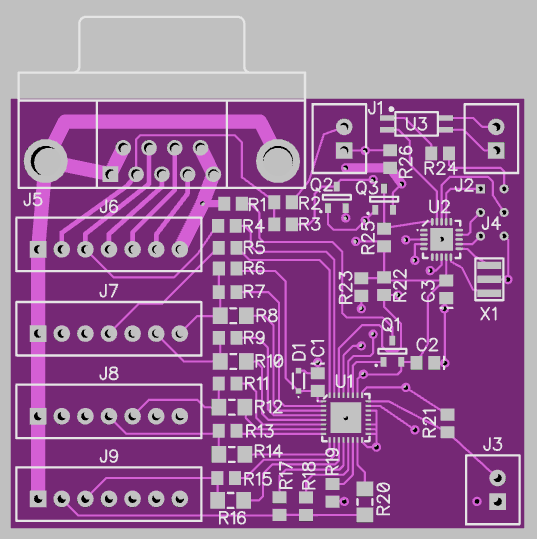

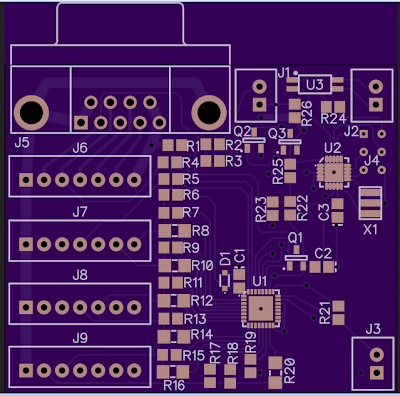

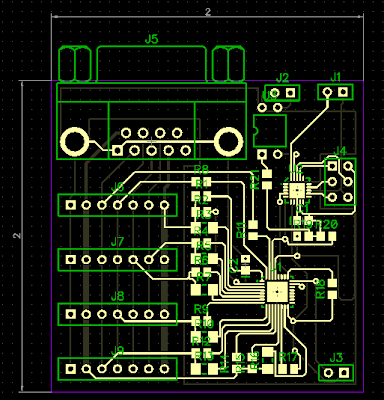

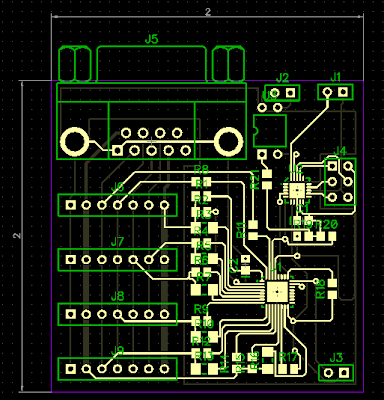

Here are some screencaps that show what it looks like. Schematic, and then the PCB layout.

I see the ceramic resonator is still missing, I haven't found or made one of those yet. The layout has very few vias, it has been reorganized for that. The ground plane is not poured in this capture. The layout is autorouted, so the traces have not been widened up for current handling except for two there that are still locked from earlier experimenting. I'll tune the routing later, right now I re-autoroute frequently so don't want to customize things yet.

Here's the essence of this design at this point:

Intersil ISL94208 6S front end chip with analog mux/offset/scaling, balance driving FETs (not using the charge/discharge control part of the chip)

AVR Micro, 16K with TWI/I2C and real USART for easy serial and standard ISP pads for programming

Daisy chained optically isolated serial connections, in and out, resonator to make serial stable without calibration

Resistors for balancing, but the current will have to be kept low enough to avoid heat issues, "Gentle Balancing", probably 50 mA or so

AVR is powered off when the board goes into sleep, current per cell should be less than a few 10's of microamps at room temperature

Intersil chip is woken up by incoming serial, AVR chip is then powered by the Intersil chip's 3.3V regulation system

The master will wakeup and query these slave battery interface boards, requesting data and sending them balancing instructions

The plan is for these slave boards to time out and shut down if they are not being communicated with

One slave board will be required for each parallel 6S group, so 12S would require 2 boards, 18S - 3, 24S - 4

Connectors for 4 parallel 6S packs on each slave board (JST-XH)

More than 4 parallel packs is possible by using cabling or external paralleling boards for the balance lines.

The master can be most anything like a common Arduino or Teensy or Raspbery Pi, lots of possibilities there

DB9 is a diagnostic port for tapping into the cells for external measurements and balancing (don't plug in your pc serial here )

)

Connector for thermistor for pack temperature monitoring is provided, thermal shutdown possible in software

Board is about 2x2 inches, small enough to integrate closely with the pack

Any questions, comments or suggestions appreciated.

The pc board layout is pretty near complete, but I need to "do it right" and enter a schematic. So I started that yesterday.

I've just about finished the schematic already. It went pretty fast, though there are still incomplete items like some of the pad layouts. The library has a lot of parts, but often not the ones I need. DipTrace has very good tools for making parts so it doesn't take long to make or adapt one for what is needed. I haven't read the documentation, but occasionally a Google search is useful to answer a question.

Here are some screencaps that show what it looks like. Schematic, and then the PCB layout.

I see the ceramic resonator is still missing, I haven't found or made one of those yet. The layout has very few vias, it has been reorganized for that. The ground plane is not poured in this capture. The layout is autorouted, so the traces have not been widened up for current handling except for two there that are still locked from earlier experimenting. I'll tune the routing later, right now I re-autoroute frequently so don't want to customize things yet.

Here's the essence of this design at this point:

Intersil ISL94208 6S front end chip with analog mux/offset/scaling, balance driving FETs (not using the charge/discharge control part of the chip)

AVR Micro, 16K with TWI/I2C and real USART for easy serial and standard ISP pads for programming

Daisy chained optically isolated serial connections, in and out, resonator to make serial stable without calibration

Resistors for balancing, but the current will have to be kept low enough to avoid heat issues, "Gentle Balancing", probably 50 mA or so

AVR is powered off when the board goes into sleep, current per cell should be less than a few 10's of microamps at room temperature

Intersil chip is woken up by incoming serial, AVR chip is then powered by the Intersil chip's 3.3V regulation system

The master will wakeup and query these slave battery interface boards, requesting data and sending them balancing instructions

The plan is for these slave boards to time out and shut down if they are not being communicated with

One slave board will be required for each parallel 6S group, so 12S would require 2 boards, 18S - 3, 24S - 4

Connectors for 4 parallel 6S packs on each slave board (JST-XH)

More than 4 parallel packs is possible by using cabling or external paralleling boards for the balance lines.

The master can be most anything like a common Arduino or Teensy or Raspbery Pi, lots of possibilities there

DB9 is a diagnostic port for tapping into the cells for external measurements and balancing (don't plug in your pc serial here

Connector for thermistor for pack temperature monitoring is provided, thermal shutdown possible in software

Board is about 2x2 inches, small enough to integrate closely with the pack

Any questions, comments or suggestions appreciated.