These days I've been studying the pros and cons of going fully digital here.

By fully digital I mean removing all the analog sensing in favour of using voltage and current sensors with digital outputs.

A sensor with such digital output, usually delta sigma, requires some digital filtering that can only be performed with dedicated hardware. Some microcontrollers, including a very close brother of this stm32f405 have this piece of silicon built in, but I don't want to change this MCU, its really hard to migrate these things.

Plan B is adding a small FPGA, it could even be a CPLD.

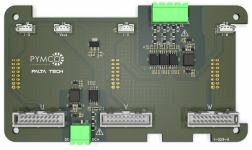

To have a quick glance at the difference between the actual analog sensing

And its digital counterpart

View attachment 1

So 2 chips (fpga+flash) can replace a big chunk of this board bill of materials. I'd add a buffer to protect the fpga, but still, it looks like an upgrade.

Anyway its not about the cost, its about being able to get send digital sensor data instead of analog. Having 1000 Amps switching close to the sensors makes it difficult to arrange the wiring in a way that doesn't pick up much noise. Its MUCH easier if the data is digital, you have pretty much no noise picked up along the way. For example, false triggering a digital bit would take something like 0.6v or more. And a single bit error is just a least significant bit error. If it were an analog with 5v=1000A 0v=-1000A, it would be a 240 Amp glitch error.

Plus, all those opamps, resistors and capacitors have their tolerances, temp drift, etc. The fpga would have none of this.

I only know verilog to configure the fpga. Well, I used to know. I could get my hands on this little board to give it a try before commiting to this http://gnarlygrey.atspace.cc/development-platform.html

Its 8usd shipped.

So I would have to write a sinc3 filter in verilog and instantiate one filter per input (3 phase currents, 3 phase voltages and bus voltage)

According to the internet®, it would look something like this

It compiles, but I should set up a testbench to properly test it. TI suggests a 128 downsampling that is not present in this code.

The filtering takes very few logic gates, its tempting. The data would be send via SPI to the MCU via DMA.

Just some brainstorming that I wanted to get written down.