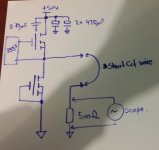

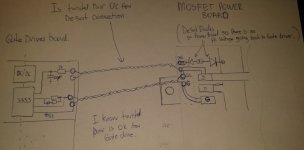

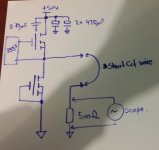

I spend most of the weekend doing Desat tests , I made a basic 1/2 bridge setup and

fitted my gate driver to the Hiside FET and then connected the G/D of the Lowside fet together to

keep it off. I then used a old PCB from one of my customers, and converted into a Pulse generator.

Using a trim-pot I could adjust the output pulse width from 3uS to 60uS which was triggered by

pressing the button. I also had a input to look at the Desat fault output from the 333J which

would turn on some LEDs when a desat fault occurred.

View attachment 2

After doing some tests I overloaded the 200Amp current sensor, so added a 0.005ohm resistor

for a current shunt and measured Desat currents around 250amps into a 10uH inductor.

The pulse width was 30uS and the desat kicked into action around 25uS.

After confirming the circuit was working, I disabled the extra comparator circuit I added

and just used the desat feature of the 333J.

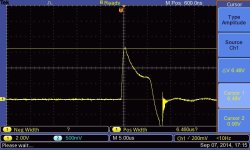

I then replaced the coil with a short-circuit and with a supply voltage of

50V I was getting currents upto 800- 900Amps ???. Shutdown times where around 7uS so I changed the

Desat cap to 33pF and got the Desat shutdown time down to 5uS.

I was very,very surprised with the currents I was seeing. I done this test up to 30times and

the FET is still working.

I then looked at the switching speed with the scope connected to the Source of the hiside

and it was around 200nS. From reading posts on ES this maybe a little bit to fast?

so added a GS cap of 10nF and it made no differents (did not try any higher values).

(gate resistor, 30ohms On, and 10ohms off)

I will play with this more when I build the controller if I need to slow down the switching due to spikes or ringing.

View attachment 1

I was using 2 x 470uF caps for these tests, so removed one of them which dropped the Desat current by approx 100amps So I saw an issue with having too much DC link caps. I still need to learn how to calculate the DC cap capacitance but I think even one 470uF cap is to much.

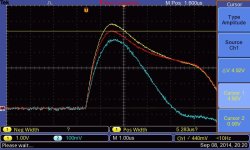

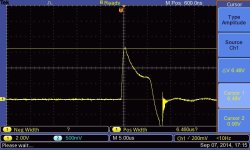

So I did one more crazy test. I added the 0.005ohm resistor between Lowside fet and GND

and turned on the lowside fet using a battery. I pressed the pulse button

to turn on the Hiside fet and saw a peak current of 1200amps. Are these currents real?

Whats going to happen if I made a controller running up to 100V in the future. The desat currents would be crazy hi.

View attachment 3

I also did the same test above without the 0.005ohm resistor and connected the scope across the DS of the Lowside fet

and used it as a 2mOhm resistor but got some silly value of like 2000amps so decided this reading was a bit dodgy. :?

Voltage across 5mOhm resistor from Crazy test above.

One more test I did was to heatup the driver board while connected to the 10uH coil.

at room temperature desat triggered at 244amps, and with the driver board to 60°C

desat current only dropped by 20amps.

So after this weekend I have decided to not worry about the extra circuit I made to make the Desat threshold more stable ,

I can now make my gate driver board smaller, and maybe I am getting to worried about the desat current in a shoot through event.

I have all ready showed the fet can handle lots of shoot through at those mad currents a number of times and its still going.

I am picking there are lots of controllers out there with not desat and the ones I have heard of , peters running for 1.5years , Lebowski's 10,000kms

are still going , so the number of times desat could occur are so small , my controller could last many years.

Its still nice to know I cannot ?

blow it up.

I will start building the power stage and then it may take some time to get use to using the dsPIC, as the last time I used one was 6years ago.

Time to watch DoctorWho now.

the bigger the fuse the louder the bang, 30A is already a firecracker !