I've been spending a lot of time working on a new layout, a very large parallel layout of 11 TO-247 devices. I've been taking notes on every lab that I have been doing with lots of scope screen shots. I would strongly suggest that you take lab notes as they really help you form a picture. I've found my best notes are taken as I'm going vs summarizing afterwards. One Note from Microsoft is an awesome solution.

Anyways, the reason I came here...

So I wanted to show everyone this neat math trick to help them calculate their approximate layout inductance since it's quite difficult to measure directly. When doing the below test I suggest using a few different values of Cadd and then averaging the results as it's not a perfect method.

Step 1. measure ringing freq

Step 2. add a known capacitance drain - source

Step 3. measure ringing freq again

Step 4. math

f_ring0 = 22MHz

f_ring1 = 15MHz

C_add = 2nF

f_ring = 1/(2pi * sqrt(Llk * Clk))

With some algebra we end up with

Clk = Cadd / (x^2 -1)

x = f_ring0 / f_ring1

1.467 = 22MHz / 15MHz

2nF / (1.467^2 - 1) = 1.736nF <--- this is the about the parasitic capacitance of your layout

Clk = 1.736nF

1/(2*pi*22Mhz)^2 * 1.736nF = 30.2 nH <-- this is about what your parasitic layout inductance is

Llk = 30.2 nH

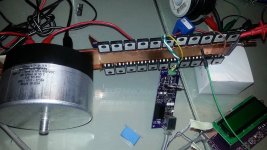

*When doing any pulse testing with an inductor, make sure it's several feet away from your measurement setup so that the magnetic field does not distort your readings. I moved my inductor about 5' away and placed it on the floor using some 8 gauge jumper cables.

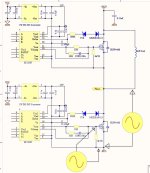

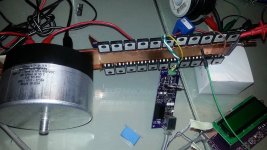

While I am using parallel devices and you are not, most of what I am saying here is applicable. This is the layout I'm working with. I've managed to get the layout inductance <70nH on two of these. With 5 parallel devices I measured 49nH and then with all 11 devices in I measured 69nH. This was designed paying careful attention to layout loop area due to being quite long. If the above numbers hold true (need more testing) then each additional MOSFET in parallel adds 3.33nH of inductance. Working backwards this means the layout by iteself ~32.3nH since 11*3.3nH = 36.6nH. Not too bad considering there is ~170mm of bus length from DC link cap to the last MOSFET. The lower you can get your layout inductance, the less you will have to deal with ringing issues.

Minimize loop area everywhere you can!

I've observed that turn on ringing is significantly reduced as I turn on the devices faster. That is I see more turn on ringing on my double pulse testing with a 1000ns switch time than I do at 500ns. I'm not certain on this observation yet as I have not mentally worked through the MOSFET turn on operation and all it's elements (such as the LC tank circuits it creates) yet as I have with turn off ringing cause / effect. I have also seen that the load inductance will cause the turn on ring to vary in amplitude but not frequency. The amount of bus voltage will also vary the amplitude. I found that higher bus voltage yielded lower ringing amplitude.

For double pulse testing, your total period after the initial charging of the coil should be close to 1/Fsw. If you plan to run the controller at 20kHz, then your off period after charging should be 25us and your 2nd turn on should also be 25us. This is simulating a 20kHz switching interval at 50% duty cycle. I've been using this method to evaluating current sharing between devices and it's been very useful. If you want to see how the device behaves at 10%, then set your off period for 45us and the on period for 5us. Trick is to maintain the total off/on period and just vary the duty.

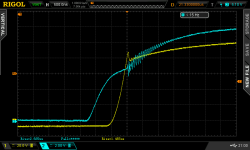

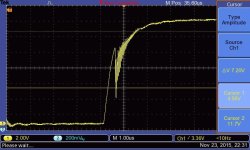

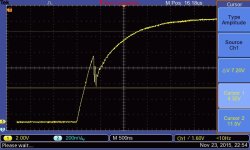

Here are some screen shots of my double pulse results for comparison. I spent a lot of time figuring out how to minimize any ringing in my layout. If you really want to get good at this it's important to spend a lot of time bench testing and playing around. Simulation is also good for this.

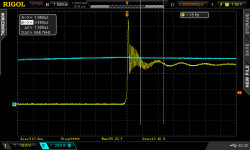

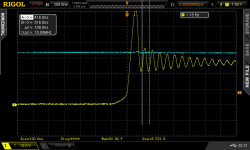

This shot shows the following

Ch1 = Drain - Source

Ch2 = off

Ch3 = total current going through array, 100mV = ~100A

Ch4 = D-S current through device in circuit (I'm using a Rogowski coil)

Math = integration of current in 2nd on period (I'm studying current sharing between devices)

This pic shows a ~500A charging of the load inductor while studying a single device. The test was done with no snubber cap and no G-S capacitance. There is a 40V over shoot (above bus voltage) D-S at turn off (I can get it < 20V pretty easily). This turn off overshoot is caused by the parastics + layout inductance. Turn on looks pretty clean.

View attachment 2

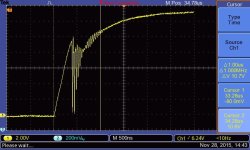

Now that I'm looking over my lab notes on this, the G-S ringing at turn on does not always translate to ringing D-S of the current waveform even though the voltage wave form can ring substantially. I found that I could significantly reduce the ringing by increase the individual gate resistors. The IRFP4568 has an internal 1 ohm resistor on the gate and I would typically add 0.47 ohms to dampen ringing. I experimented and changed them from 0.5 to 1.0 to 2.0 to 3.0 and measured each time. Every time I increased the resistance, the turn on ringing went down, but turn on time went up due to being slower. What I found was I could decrease my main gate resistor significantly which would yield a faster turn on with less ringing than if I had tried to achieve the same switch time with the 0.47 ohm resistors. It's about finding a balance.

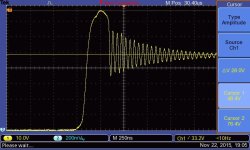

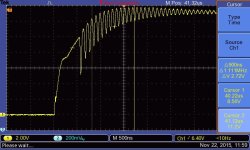

Another note I made was that my turn on ring resonance freq was slightly higher than my turn off ring, 12.5MHz on vs 11.0MHz off. This was pretty consistent across 2 different power stages I built.

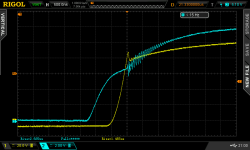

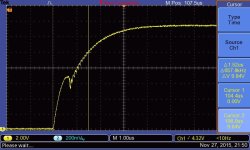

This is the turn at 80A and pretty tidy IMO.

Ch1 = Drain to Source current

Ch2 = Gate to Source voltage