zombiess

10 MW

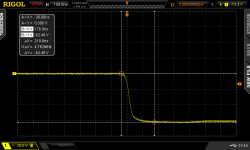

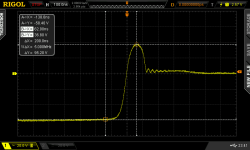

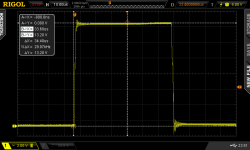

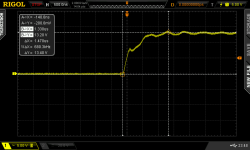

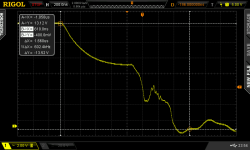

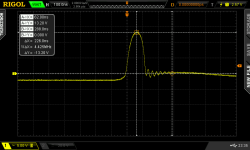

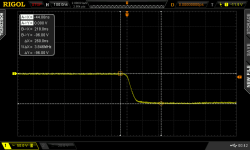

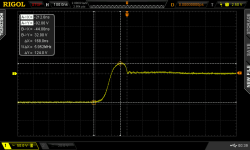

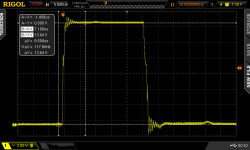

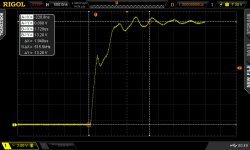

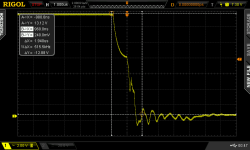

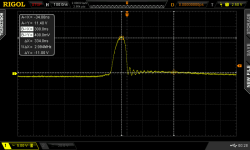

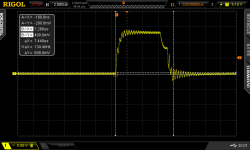

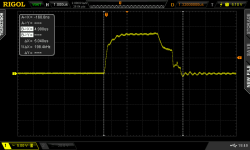

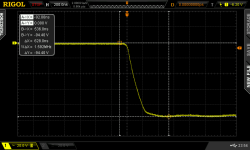

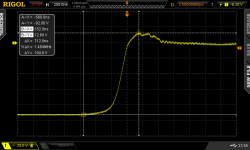

HighHopes said:take a moment to appreciate how difficult that is to obtain. let me say, not many can do that. great work so far, it is encouraging.7.2V @ 90A with 60V switching right at 200nS.

Is it good or hard to obtain?

So am I correct in saying my overshoot is only 7.2V based on how I have measured and compensating for the CMMR in the probes?

I can only take your word for it as I have VERY little experience in SMPS design, in fact this is my only experience with SMPS design, but I have done a tiny bit of hobbyist RF amp work to 450mhz before (no scope) and there are some parallels in design concepts.

I am also now second guessing my choice to use the boost stage as it appears it's much more than I really need, but time will tell the story on that. I have some IXYS 200V FETs that have a pretty big Qg.

How much of a difference would a set of differential probes make? Would it make my life easier and provide more accurate readings with less interference?

I found a set of Pintech 700V 100mhz differentials for $380 (I don't drink, smoke or gamble so buying educational things is my vice). I don't know the brand but I care little about brands if the specs are good and it works. It's not like I'm sending people into space or building medical equipment, I just would like something that does the job to the level I require.

Here is a link to the set with specs

http://www.pintech.com.cn/en/showpro.asp?id=1185&idc=1185&str=Differential%20Probe%20OEM

I am unfamiliar with differential probes but understand the concept of floating, I just modded 2 isolated power supplies to float from ground tonight by removing the earth ground reference which was tied to the neg output, I understand this is done for safety reasons, but I need pure floating goodness to put them in series and up my rail voltage! I have a pair of 120V:110V center tapped transformers which output something like 5A, they each weigh around 12lbs so I could rig up an isolation transformer (I have made one before this before with this pair) and float my entire scope, but that's a bit risky for my liking. Speaking of risky, while digging around tonight I found my HeNe power supply, I forget the specs but I know it's deadly. Bought it when I was 12 or 13yrs old to power a 5mW 632.8nm tube I use to have (I wonder what I did with my Michelson Interferometer I built in HS?).