zombiess

10 MW

Njay said:It means is just real.zombiess said:The resemblance is remarkable, but is it a function of the desat or the probes?

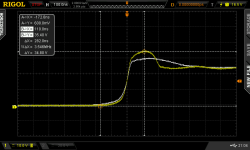

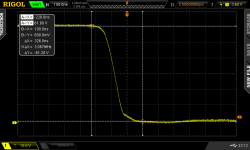

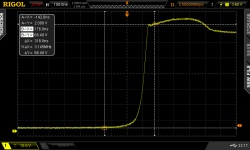

I had never seen the rounded hump before, but my experience is very reduced. Maybe something to do with the very fast current switching. It's like the diode took some time to turn on, then when it did it drastically reduced the voltage raise creating the hump. I don't know, but looks like bad news because the overshoot is just huge.

lol, I wish!!...HighHopes said:(you stole my thunder Njay, you're too good! lol).

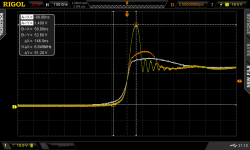

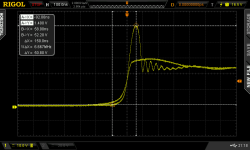

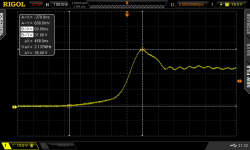

Check out my single FET D-S at 70A 96V and then the very last pic I posted of 4 parallel FETs at 325A 96V. With just one FET the mystery hump is coming in at 124V. With 4 parallel and 5x the current flow the hump is only 104V. The switching is much slower on the 4 parallel FETs, so I need to determine if the size of that hump is being controlled by the paralleling of the FETs or the switching speed. I did notice that if I kept my current flow around 70a and added FETs in parallel the hump reduced and the small amount of ringing completely disappeared. The ringing frequency got lower as FETs were added.

Even if the hump is real, it's not a percentage of the buss as it appeared. At 104V it's very manageable. I would like to be able to max out the voltage on this controller at 125V, but I'm not sure if that will happen, it does look like it will be successful at 100V buss which is my main target. Once I change gate resistors I'll be able to see if that spike/hump is switching speed related.