zombiess

10 MW

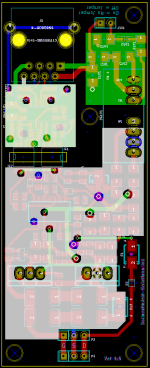

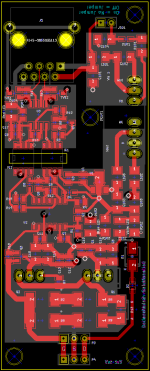

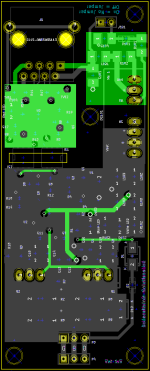

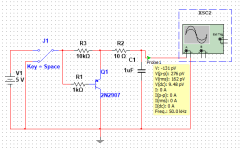

I started working on this gate driver design about 2 weeks ago. I've been working to improve on the previous and now I'm starting to experiment a little. This gate drive is being designed to drive a large bank of parallel MOSFETs for a controller idea I'm testing out. It's going to be in what could be considered a harsh EMI environment.

Right now this is just a draft, but I'm hoping to have the boards produced soon so that I may start slaving away with the soldering gear and some tweezers. As much as I want to rush into building this, I know better.

I'm trying to get a part justification write up done to explain things that might not be obvious. Right now only 1/2 of the differential setup is visible, the other side is placed on the controller board.

The PWM signal and the fault out from the gate drive and +5v and +24V are being carried over CAT6 shielded twisted pair. That provides 8 conductors and one shield.

2 for PWM (differential)

2 for Fault (differential)

2 for +24V

2 for +5

Since there are 6 gate drivers for a 3 phase setup, there will be six CAT6 cables running to the controller. I anticipate the length being ~1m, maybe 0.5m.

The reason for differential signaling is it has very high CMRR. CMRR = Common Mode Rejection Ratio. I chose to go with an RS485 driver chip as I believe it fit the need well and comes in a neat little package requiring very few additional parts. I added some TVS diodes to improve the static sensitivity, because the cables will be handled more often than I would like.

Posted up are KiCAD files and PDFs of the board layout and schematic. Sorry about the super thin traces in the PDFs, that's a KiCAD bug. Some of the voltage call outs are incorrect as I used specific vs generic names, then changed the voltage converter from 15V to 12V... my bad, need to edit that.

Post up questions if you got them.

Right now this is just a draft, but I'm hoping to have the boards produced soon so that I may start slaving away with the soldering gear and some tweezers. As much as I want to rush into building this, I know better.

I'm trying to get a part justification write up done to explain things that might not be obvious. Right now only 1/2 of the differential setup is visible, the other side is placed on the controller board.

The PWM signal and the fault out from the gate drive and +5v and +24V are being carried over CAT6 shielded twisted pair. That provides 8 conductors and one shield.

2 for PWM (differential)

2 for Fault (differential)

2 for +24V

2 for +5

Since there are 6 gate drivers for a 3 phase setup, there will be six CAT6 cables running to the controller. I anticipate the length being ~1m, maybe 0.5m.

The reason for differential signaling is it has very high CMRR. CMRR = Common Mode Rejection Ratio. I chose to go with an RS485 driver chip as I believe it fit the need well and comes in a neat little package requiring very few additional parts. I added some TVS diodes to improve the static sensitivity, because the cables will be handled more often than I would like.

Posted up are KiCAD files and PDFs of the board layout and schematic. Sorry about the super thin traces in the PDFs, that's a KiCAD bug. Some of the voltage call outs are incorrect as I used specific vs generic names, then changed the voltage converter from 15V to 12V... my bad, need to edit that.

Post up questions if you got them.