mxlemming

100 kW

- Joined

- Jul 17, 2020

- Messages

- 1,209

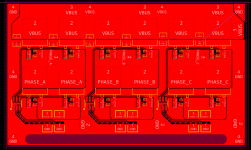

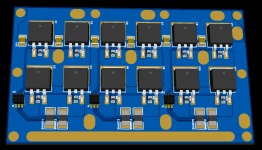

I thought I explained well and shared screenshots of the layout... Are you asking for the complete KiCAD source files? I'm not planning on publicly sharing them. I'll share them with individuals for personal use, not production and sale.Greeting.

I am very interested in using IMS for power stage but haven't try one yet.

IMO the main obstacles to me seems to be it's hard to router with only one layer but still keeps signal trace away power path.

Would you kindly share and explain your design so that I will learn a lot and made much less stupid mistakes.

It's a standard 5$ option on jlcpcb. I already made green and black ones so purple seemed worth the extra 2 days turnaround...BTW normally for aluminum PCB, white is the default color for solder mask, did you pay extra bucks for purple?

I didn't recognize it in the first glance.

Last edited: