ARod1993

100 W

I've been lusting after an Emrax 188 for a while; the only concern I have is figuring out how to run it/what controller to run it with. I saw Ben Katz's teardown of the 228LV here: https://build-its-inprogress.blogspot.com/2017/05/emrax-motor-teardown.html and the first thing he mentions is the ridiculously low resistance and inductance (1.12mOhm and 10uH) and a suggested PWM frequency of 100kHz or so to limit current ripple; the only problem is that 100kHz PWM switching is difficult with modern Si MOSFETS.

If we look at the IPT059N15N3ATMA1 (a modern 150V 150A SMT device, datasheet here for reference: https://www.infineon.com/dgdl/IPT059N15N3+G_Rev1.1.pdf?folderId=db3a304326623792012669f6bee2224b&fileId=db3a30433e9d5d11013e9e62778d0185 ) they list turn on time as 35ns and turn-off time as 14ns; if we assume that the switch voltage rise and current drop are linear, you wind up with a triangle whose area is (rise time+fall time)*(peak power per switch)/2. Assuming a 30s pack at 100A per switch, the total loss per switching event is (49ns)(12kW)/2= 294uJ per cycle, which corresponds to about 30W per switch; on a 30-fet controller that translates to 900W of power wasted in switching losses. The I^2R loss per device comes out to (100A^2*0.0059)=60W per device, with a maximum of 1800W in conduction losses, giving about 2.7kW wasted out of 50kW (95% efficiency; not great, not terrible)

In gallium nitride this would be a lot easier to do; the EPC2033 eGaN transistor is also rated for 150V, but has a total gate charge of only 3.2nC (as opposed to the 24nC gate charge required to switch the IPT059N15N3ATMA1 ), which means a 2A driver could conceivably switch them on and off in 1-1.5ns. They also apparently parallel quite nicely, with a positive temperature coefficient. The down side is that they're $8 each, and top out around 30A each, which means for a 450-500A controller you'd need 90-100 devices (which means spending $800 or so on the raw transistors before you do anything else). At that point each device is dissipating (3ns)(120V*30A)/2= 5.4uJ per device, which at 100kHz is 0.54W, or 54W switching loss across an entire 500A controller. Assuming you run your devices at the full 30A all the time, your conduction losses per device are (30A^2*0.007) is 6.3W per device, or 630W total, bringing your total controller losses at 50kW to about 700W (which translates to 98.6% efficiency; much better)

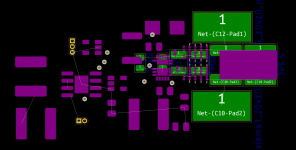

The downside to running GaN in this way is that the power transistors are 4.6mm x 2.6mm 24-BGA dies, and keeping them cool is both important and interesting. The thermal resistance of the GaN dies to the board is 4C per watt junction-to-board assuming each FET gets a square inch of copper board all to itself; if you want to get good cooling performance you could probably push things significantly farther if you mounted a heatsink to the top of the board (they claim 0.45C/W junction-to-case, but then if you use their recommendations for thermal interface materials you get 4.7ish C/W across the top junction, so your total resistance out the top is 5.1C/W. If you use the devices as rated at 30A each that comes out to 6.84W(5.1C/W) or about 30C temp rise above ambient, which isn’t bad. Then it’s a matter of actually driving the FETs, which require a special GaN driver (GaN gates blow through at about 6V, so you need a driver that’s designed to prevent that from happening) that costs about $4 per driver. For a 50kW controller that’s another $200ish of driver chips to make everything work, and laying all this out on a board is going to get really entertaining really fast.

The other alternative would be to use a soft-switched motor driver; they exist and I've seen them in papers, but they're uncommon, wonky, and low power thus far. There's apparently a startup that's commercializing them, but they're actually using an AI to control the preresonant circuit: https://www.electronicsweekly.com/news/design/pre-switchs-soft-switching-power-inverter-2021-04/ I was wondering if any of the old hands on here had any experience with this sort of stuff, and what people's thoughts were on these sorts of controllers?

If we look at the IPT059N15N3ATMA1 (a modern 150V 150A SMT device, datasheet here for reference: https://www.infineon.com/dgdl/IPT059N15N3+G_Rev1.1.pdf?folderId=db3a304326623792012669f6bee2224b&fileId=db3a30433e9d5d11013e9e62778d0185 ) they list turn on time as 35ns and turn-off time as 14ns; if we assume that the switch voltage rise and current drop are linear, you wind up with a triangle whose area is (rise time+fall time)*(peak power per switch)/2. Assuming a 30s pack at 100A per switch, the total loss per switching event is (49ns)(12kW)/2= 294uJ per cycle, which corresponds to about 30W per switch; on a 30-fet controller that translates to 900W of power wasted in switching losses. The I^2R loss per device comes out to (100A^2*0.0059)=60W per device, with a maximum of 1800W in conduction losses, giving about 2.7kW wasted out of 50kW (95% efficiency; not great, not terrible)

In gallium nitride this would be a lot easier to do; the EPC2033 eGaN transistor is also rated for 150V, but has a total gate charge of only 3.2nC (as opposed to the 24nC gate charge required to switch the IPT059N15N3ATMA1 ), which means a 2A driver could conceivably switch them on and off in 1-1.5ns. They also apparently parallel quite nicely, with a positive temperature coefficient. The down side is that they're $8 each, and top out around 30A each, which means for a 450-500A controller you'd need 90-100 devices (which means spending $800 or so on the raw transistors before you do anything else). At that point each device is dissipating (3ns)(120V*30A)/2= 5.4uJ per device, which at 100kHz is 0.54W, or 54W switching loss across an entire 500A controller. Assuming you run your devices at the full 30A all the time, your conduction losses per device are (30A^2*0.007) is 6.3W per device, or 630W total, bringing your total controller losses at 50kW to about 700W (which translates to 98.6% efficiency; much better)

The downside to running GaN in this way is that the power transistors are 4.6mm x 2.6mm 24-BGA dies, and keeping them cool is both important and interesting. The thermal resistance of the GaN dies to the board is 4C per watt junction-to-board assuming each FET gets a square inch of copper board all to itself; if you want to get good cooling performance you could probably push things significantly farther if you mounted a heatsink to the top of the board (they claim 0.45C/W junction-to-case, but then if you use their recommendations for thermal interface materials you get 4.7ish C/W across the top junction, so your total resistance out the top is 5.1C/W. If you use the devices as rated at 30A each that comes out to 6.84W(5.1C/W) or about 30C temp rise above ambient, which isn’t bad. Then it’s a matter of actually driving the FETs, which require a special GaN driver (GaN gates blow through at about 6V, so you need a driver that’s designed to prevent that from happening) that costs about $4 per driver. For a 50kW controller that’s another $200ish of driver chips to make everything work, and laying all this out on a board is going to get really entertaining really fast.

The other alternative would be to use a soft-switched motor driver; they exist and I've seen them in papers, but they're uncommon, wonky, and low power thus far. There's apparently a startup that's commercializing them, but they're actually using an AI to control the preresonant circuit: https://www.electronicsweekly.com/news/design/pre-switchs-soft-switching-power-inverter-2021-04/ I was wondering if any of the old hands on here had any experience with this sort of stuff, and what people's thoughts were on these sorts of controllers?