Dear All,

I would like first to thank all the members on this forum who shared their knowledge on FOC control design.

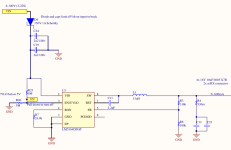

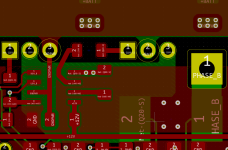

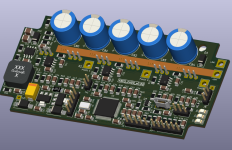

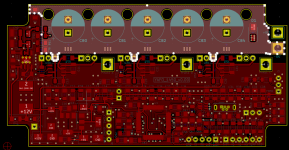

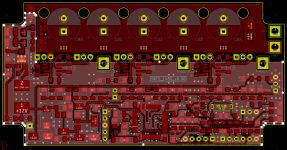

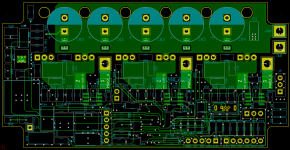

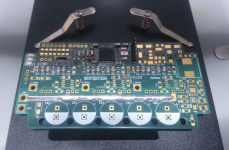

Finally, after investigation around MP2-ESC, Cheap FOcer, A200S, and other VESC-compatible HW, I have decided to design my ESC with the following constraints:

- Reliability/Robustness on top priority

- 14s Battery

- 50 Amps per phase

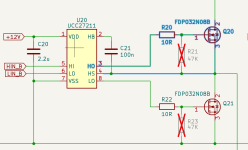

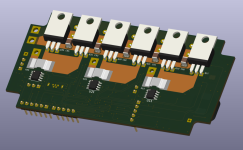

- TO 220 FET's

- Classic 8 pin drivers for each leg.

- Ease of DIY soldering AND servicing.

- No fine pitch components, except MCU (no choice !)

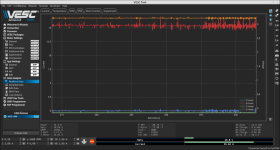

- Running VESC FW compiled with the appropriate parameters set

- Full compatibility with VESC tool

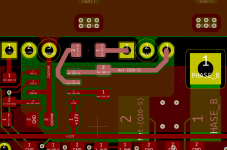

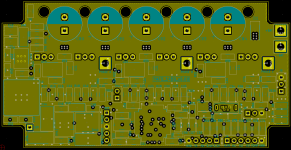

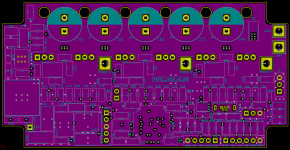

- 4 layer design PCB

- HAMMOND 1490WB Aluminum enclosure (106mm x 54mm pcb size)

So, here is the first draft of the schematic and any feed back will be welcome.

I would like first to thank all the members on this forum who shared their knowledge on FOC control design.

Finally, after investigation around MP2-ESC, Cheap FOcer, A200S, and other VESC-compatible HW, I have decided to design my ESC with the following constraints:

- Reliability/Robustness on top priority

- 14s Battery

- 50 Amps per phase

- TO 220 FET's

- Classic 8 pin drivers for each leg.

- Ease of DIY soldering AND servicing.

- No fine pitch components, except MCU (no choice !)

- Running VESC FW compiled with the appropriate parameters set

- Full compatibility with VESC tool

- 4 layer design PCB

- HAMMOND 1490WB Aluminum enclosure (106mm x 54mm pcb size)

So, here is the first draft of the schematic and any feed back will be welcome.