You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

A PIC based Battery Management System

- Thread starter fechter

- Start date

lostcoyote

10 W

- Joined

- Aug 26, 2008

- Messages

- 72

Okay randomly and lostcoyote. Good ideas percolating. I'll put together a test of the Atmega168 10-bit A/D with 6-channel mux to see how well the dirt-cheap/low-res approach works. Suggestions on low-precision resistor values to drop 80-volts to about 5-volts? Noise reduction?

Randomly's LT1990 amp chip is tempting -- robust, but expensive. I'll keep it in mind. For a single unit the price isn't bad. Though coming up with something more elegant would be nice.

Scaling is easy and cheap with voltage dividers. Shifting cell potentials to zero is easy with the MCU, but sacrifices resolution. What about subtraction of voltages before the A/D? Op amps? How costly and complex would that be per cell? Subtract cell #19 from cell #20 and you have the voltage of 20 at common ground. Simple. Full A/D resolution per cell. Similar to the expensive differential amps without the extra features and cost. Or perhaps there's another way to do a simple voltage subtraction.

Thanks

Richard

Randomly's LT1990 amp chip is tempting -- robust, but expensive. I'll keep it in mind. For a single unit the price isn't bad. Though coming up with something more elegant would be nice.

Scaling is easy and cheap with voltage dividers. Shifting cell potentials to zero is easy with the MCU, but sacrifices resolution. What about subtraction of voltages before the A/D? Op amps? How costly and complex would that be per cell? Subtract cell #19 from cell #20 and you have the voltage of 20 at common ground. Simple. Full A/D resolution per cell. Similar to the expensive differential amps without the extra features and cost. Or perhaps there's another way to do a simple voltage subtraction.

Thanks

Richard

lostcoyote

10 W

- Joined

- Aug 26, 2008

- Messages

- 72

rf,

randonly get's all the credit here.

i'm just putting up some pretty pictures.

btw, i didn't include a charge current source (PIC controlled) in the block diagram above. just the shunt control/feedback stuff.

randonly get's all the credit here.

i'm just putting up some pretty pictures.

btw, i didn't include a charge current source (PIC controlled) in the block diagram above. just the shunt control/feedback stuff.

The schematic looks pretty good. You can drop the bottom LT1990 and read the lowest cell voltage directly. You also can just go with the 10 bit A/D in the cpu which will give you ~5mv resolution. 12 bit isn't really necessary.

You are always going to have the slow battery drain from the Diff amp input resistors, I believe they are 1 M ohm. So it's not something I'd leave on the pack in the closet for a year. You'll also need to make up for the slow unbalancing of the cells since the lowest cells will be drained faster by the diff amp resistors. So your balancing will have to do a little more work on charge than otherwise.

For the mux you can use a couple of 74HC4051 8:1 Muxs. They have 3 channel select lines and an enable line. So it'll cost you one more I/O line out of the CPU than a 16:1 mux but they are dirt cheap and you can even add a third 74HC4051 if you want to handle 24 cells.

You are always going to have the slow battery drain from the Diff amp input resistors, I believe they are 1 M ohm. So it's not something I'd leave on the pack in the closet for a year. You'll also need to make up for the slow unbalancing of the cells since the lowest cells will be drained faster by the diff amp resistors. So your balancing will have to do a little more work on charge than otherwise.

For the mux you can use a couple of 74HC4051 8:1 Muxs. They have 3 channel select lines and an enable line. So it'll cost you one more I/O line out of the CPU than a 16:1 mux but they are dirt cheap and you can even add a third 74HC4051 if you want to handle 24 cells.

lostcoyote said:i'm just putting up some pretty pictures.

and they are pretty. I'm curious as to what software you are using to generate them? Although I suspect the fact that they look so good is more dependent on your good artistic sensibilities. nice work.

lostcoyote

10 W

- Joined

- Aug 26, 2008

- Messages

- 72

lol - power point - lol

i do RF subsystem charts at work quite often.

i wouldn't suspect that a 1M drain would hurt too much - if you're not using the batteries for a year, might as well disconnect the BMC.

i do RF subsystem charts at work quite often.

i wouldn't suspect that a 1M drain would hurt too much - if you're not using the batteries for a year, might as well disconnect the BMC.

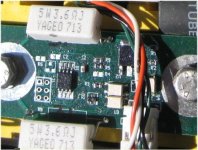

Here's somebody that is using the one processor per cell approach. I still think this is the way to go. It's an ATiny 4x something from Atmel. I can see some optocouplers and about a 2 amp shunt resistor set. It uses a I2C bus to communicate to the main unit. There was a display that showed the cell voltages sequentially and showed the highest and lowest cell voltage and cell number. Cool. Quoted around $20 per cell.

Zoom in:

Zoom in:

Ok, here's a scheme to sample the cell voltages for the A/D converter on a single MCU system without having any current drain on the cells when you aren't actually reading them. The schematic is not complete, it's just enough to explain the concept, you'll need to add the rest of the cells and the MCU etc.

The concept takes advantage of the fact that the MCU A/D converters only need a couple of uSec aquisition time and then it goes off and does the conversion. So we only need to present the cell voltage for several microseconds to the A/D converter at the beginning of each conversion.

We connect a capacitor across a cell (C1) through a pair of resistors (R3, R4). The capacitor charges up through the resistors until it's voltage matches the cell voltage. To read that voltage we pull the bottom of the capacitor to ground with an FET (Q2). Now the bottom of the cap is at ground, the top of the cap needs to be connected to the A/D. We do that with another FET (Q3).

Since the source of Q3 can be up to 4.3V above ground we need to have a gate drive that is greater than 4.2V + gate threshold voltage. BS107A has about 3V gate threshold voltage. A 10V gate drive should do the job. The gate drive is a 10V supply connected to our selected pair of FETs through an 1:8 MUX 4051. To control the Mux from the MCU with it's 5V logic lines we need a level translator, the 4504. The MCU selects the appropriate line with the 3 address lines (A,B,C) and then pulls the appropriate INHIBIT line low to enable that MUX. With 3 address lines and 3 different chip inhibit lines we can access up to 24 different cells using 6 port lines. The MUX channel turns on, pulls the gates of the two FETs up to 10V and this pulls the Bottom of the cap to ground, and connects the top of the cap to the A/D input of the MCU. We wait the appropriate aquistion time, start the A/D conversion, then Pull the INHIBIT line High again to remove the 10V gate drive. The 10K pull down resistor turns the FETs off and the cap floats back up to the cell voltage. The resistors also keep the gates turned off when the whole system is shut down.

The 10V supply doesn't need to be exactly 10V it could be just tapping off the top of the third cell in the pack with a 1K resistor and bypassing that to ground with a 0.1uF cap and that should be good enough down to 2V cell voltages.

The FETs are BS107A, they can handle up to 200V, are cheap, available in a TO-92 package if you want. They have an on resistance around 5 ohms. In the worst case where it's pulling down the two 100K resistors from a cell that's around 90V in the pack it'll have to flow about 1.8mA and it will pull the bottom of the cap to within 9mV of ground. You can use a FET with a lower on resistance if that's not acceptable, (or just correct for it in software). Remember you don't want a FET with too much gate capacitance as it will slow down the turn on/off.

The problem area is that when you pull the cap down to ground it's going to start rapidly charging up through the top resistor. We minimize that problem by choosing our cap and resistor large enough that the voltage increase is small in the 10 uSec we have it pulled down to sample with the A/D. However we don't want to choose our RC to be too slow or it won't track the cell voltage fast enough. 100K and 0.1 uF with 6 volts across the resistor will increase by 6mv in the 10 uSec sampling time.

Most of the cells will have the cap charging up to the cell voltage through three 100K resistors, which gives us about a 30Hz response to changing cell voltages which should be good enough.

However if there were 90V across that resistor the cap voltage would change by 90mv in that 10usec. Not too good. So we add a voltage clamp (R7 and Q10). The reverse connected transistor just acts like a zener diode with about an 8 Volt breakdown voltage. Using a transistor instead of a zener in this case helps because below the breakdown voltage the reverse leakage current is very small and won't mess up our readings.

So now with the clamp in the higher voltage cells we won't see any worse than about a 6mV shift in our 10usec window.

The other thing we have to pay attention to is duty cycle. Whenever we have the cap pulled down it is charging up above the actual cell voltage it's supposed to be tracking. When we release it, it takes time for that voltage to drop back towards the actual cell voltage. If our sampling duty cycle is 1/1000 that will reduce that voltage offset by 6v/1000 or about 6mv. So if we sample at 100 times a second for 10 uSec at a time the cap will average about 6mV above the actual cell voltage. Sampling at 50 times a second would reduce that to 3mv error.

There are probably other ways to generate the gate drives (if you have 24 I/O lines you could just buffer them through four 4504 voltage translators) but this should work, parts are available in DIP form, and it's cheap. The bottom cell just has a single FET to connect it directly to the A/D input. This all assumes the MCU is running on 5V supply. The second cell doesn't need a voltage clamp.

The concept takes advantage of the fact that the MCU A/D converters only need a couple of uSec aquisition time and then it goes off and does the conversion. So we only need to present the cell voltage for several microseconds to the A/D converter at the beginning of each conversion.

We connect a capacitor across a cell (C1) through a pair of resistors (R3, R4). The capacitor charges up through the resistors until it's voltage matches the cell voltage. To read that voltage we pull the bottom of the capacitor to ground with an FET (Q2). Now the bottom of the cap is at ground, the top of the cap needs to be connected to the A/D. We do that with another FET (Q3).

Since the source of Q3 can be up to 4.3V above ground we need to have a gate drive that is greater than 4.2V + gate threshold voltage. BS107A has about 3V gate threshold voltage. A 10V gate drive should do the job. The gate drive is a 10V supply connected to our selected pair of FETs through an 1:8 MUX 4051. To control the Mux from the MCU with it's 5V logic lines we need a level translator, the 4504. The MCU selects the appropriate line with the 3 address lines (A,B,C) and then pulls the appropriate INHIBIT line low to enable that MUX. With 3 address lines and 3 different chip inhibit lines we can access up to 24 different cells using 6 port lines. The MUX channel turns on, pulls the gates of the two FETs up to 10V and this pulls the Bottom of the cap to ground, and connects the top of the cap to the A/D input of the MCU. We wait the appropriate aquistion time, start the A/D conversion, then Pull the INHIBIT line High again to remove the 10V gate drive. The 10K pull down resistor turns the FETs off and the cap floats back up to the cell voltage. The resistors also keep the gates turned off when the whole system is shut down.

The 10V supply doesn't need to be exactly 10V it could be just tapping off the top of the third cell in the pack with a 1K resistor and bypassing that to ground with a 0.1uF cap and that should be good enough down to 2V cell voltages.

The FETs are BS107A, they can handle up to 200V, are cheap, available in a TO-92 package if you want. They have an on resistance around 5 ohms. In the worst case where it's pulling down the two 100K resistors from a cell that's around 90V in the pack it'll have to flow about 1.8mA and it will pull the bottom of the cap to within 9mV of ground. You can use a FET with a lower on resistance if that's not acceptable, (or just correct for it in software). Remember you don't want a FET with too much gate capacitance as it will slow down the turn on/off.

The problem area is that when you pull the cap down to ground it's going to start rapidly charging up through the top resistor. We minimize that problem by choosing our cap and resistor large enough that the voltage increase is small in the 10 uSec we have it pulled down to sample with the A/D. However we don't want to choose our RC to be too slow or it won't track the cell voltage fast enough. 100K and 0.1 uF with 6 volts across the resistor will increase by 6mv in the 10 uSec sampling time.

Most of the cells will have the cap charging up to the cell voltage through three 100K resistors, which gives us about a 30Hz response to changing cell voltages which should be good enough.

However if there were 90V across that resistor the cap voltage would change by 90mv in that 10usec. Not too good. So we add a voltage clamp (R7 and Q10). The reverse connected transistor just acts like a zener diode with about an 8 Volt breakdown voltage. Using a transistor instead of a zener in this case helps because below the breakdown voltage the reverse leakage current is very small and won't mess up our readings.

So now with the clamp in the higher voltage cells we won't see any worse than about a 6mV shift in our 10usec window.

The other thing we have to pay attention to is duty cycle. Whenever we have the cap pulled down it is charging up above the actual cell voltage it's supposed to be tracking. When we release it, it takes time for that voltage to drop back towards the actual cell voltage. If our sampling duty cycle is 1/1000 that will reduce that voltage offset by 6v/1000 or about 6mv. So if we sample at 100 times a second for 10 uSec at a time the cap will average about 6mV above the actual cell voltage. Sampling at 50 times a second would reduce that to 3mv error.

There are probably other ways to generate the gate drives (if you have 24 I/O lines you could just buffer them through four 4504 voltage translators) but this should work, parts are available in DIP form, and it's cheap. The bottom cell just has a single FET to connect it directly to the A/D input. This all assumes the MCU is running on 5V supply. The second cell doesn't need a voltage clamp.

lostcoyote

10 W

- Joined

- Aug 26, 2008

- Messages

- 72

could a switched capacitor network be employed where the switches are DPST?

so if you imagine if each leg of the capacitor is tied to common, when the switches turn to the left side pole, they attach to the battery and charge to the battery voltsge.

then switch to the right poles (one side tied to ground) and that gets fed into the ADC through a MUX (assuming input imedance of teh ADC is high or else use a voltage follower to eliminate MUX resistances from the equation)

so left = sample, right=hold (and decay)

i don't think you'd need to sample but once every 1/2 second or so... and during no use, the switches default to hold position so they're not tied to the batteries.

so if you imagine if each leg of the capacitor is tied to common, when the switches turn to the left side pole, they attach to the battery and charge to the battery voltsge.

then switch to the right poles (one side tied to ground) and that gets fed into the ADC through a MUX (assuming input imedance of teh ADC is high or else use a voltage follower to eliminate MUX resistances from the equation)

so left = sample, right=hold (and decay)

i don't think you'd need to sample but once every 1/2 second or so... and during no use, the switches default to hold position so they're not tied to the batteries.

Yes, a switched flying capacitor sampler would work but you run into the problem of finding integrated FET switches with enough voltage rating to do the job. They seem to max out at about 40V.

That's what this schematic essentially is, a flying capacitor sampler that has been simplified and made with discrete components that have enough voltage rating to do the job. We eliminate the high side switches that would normally connect the flying cap to the cell and just replace them with series resistors, then count on pulling the cap down and reading it so fast that very little voltage change occurs on the cap during that process. It should be able to handle at least a 24 Cell battery stack.

Eliminating the high side switches also eliminates the problem of level shifting the gate drive to them and reduces the complexity and parts count a lot.

It also greatly reduces the problem of common mode voltage rejection that demands such high precision matching of resistors with a Diff amp. You can reduce common mode voltage errors to whatever level you want by using a lower ON resistance FET for the pulldown FET, and/or increasing the resistor values. You can also just compensate for it in software since you can keep track of the stack voltage and thus get a pretty good idea of the current through any given pulldown FET and the voltage drop across it. You also retain full A/D resolution so a 10bit A/D is more than sufficient to give you all the resolution you need.

The advantages are that it uses cheap parts in hand solderable packages, it doesn't drain the cells at all when you are not actually reading the voltage, and the average current drain on the cells is 100 times smaller than with permanently connected resistors going to Diff amps. The pack is thus unbalanced 100 times slower than the Diff amp system.

That's what this schematic essentially is, a flying capacitor sampler that has been simplified and made with discrete components that have enough voltage rating to do the job. We eliminate the high side switches that would normally connect the flying cap to the cell and just replace them with series resistors, then count on pulling the cap down and reading it so fast that very little voltage change occurs on the cap during that process. It should be able to handle at least a 24 Cell battery stack.

Eliminating the high side switches also eliminates the problem of level shifting the gate drive to them and reduces the complexity and parts count a lot.

It also greatly reduces the problem of common mode voltage rejection that demands such high precision matching of resistors with a Diff amp. You can reduce common mode voltage errors to whatever level you want by using a lower ON resistance FET for the pulldown FET, and/or increasing the resistor values. You can also just compensate for it in software since you can keep track of the stack voltage and thus get a pretty good idea of the current through any given pulldown FET and the voltage drop across it. You also retain full A/D resolution so a 10bit A/D is more than sufficient to give you all the resolution you need.

The advantages are that it uses cheap parts in hand solderable packages, it doesn't drain the cells at all when you are not actually reading the voltage, and the average current drain on the cells is 100 times smaller than with permanently connected resistors going to Diff amps. The pack is thus unbalanced 100 times slower than the Diff amp system.

Randomly said:[...]

For the mux you can use a couple of 74HC4051 8:1 Muxs. They have 3 channel select lines and an enable line. So it'll cost you one more I/O line out of the CPU than a 16:1 mux but they are dirt cheap and you can even add a third 74HC4051 if you want to handle 24 cells.

Turns out Mouser has some 16-channel multiplexer chips (4067) that cost less than two of their cheapest 8s.

Saw an intriguing chip for $22. A high voltage (100-volt) 16-channel analog multiplexer. That and one LT1990 might do the trick. (The LT1990's gain can be MCU controlled.) Problem is the mux wants a 100-volt power supply. :-(

That flying capacitor sounds intriguing too. Not sure how that all works though.

Richard

wrobinson0413

1 kW

.

Read the thread. Per cell CPU approaches have been proposed and some people have tried implementing them. I'm not sure what the status of those projects is. Last I remember there was some problems with spikes on the supplies reseting or glitching the processors. You can use a transistor and two resistors to do the level shifting between processors for communication if you want to avoid the optoisolators.

Yes, it is burried in the thread somewhere.

One thing I'm curious about: When the processor goes to sleep, what does it take to wake it up? Can it be set on a timer to wake up by itself after a programmed amount of time? If the processors are permanently attached to the cells, I'd want to be sure they don't drain the cells during long periods of storage. With smaller capacity batteries, this would be more of an issue.

This version seems to work well, it's just too expensive....

One thing I'm curious about: When the processor goes to sleep, what does it take to wake it up? Can it be set on a timer to wake up by itself after a programmed amount of time? If the processors are permanently attached to the cells, I'd want to be sure they don't drain the cells during long periods of storage. With smaller capacity batteries, this would be more of an issue.

This version seems to work well, it's just too expensive....

Tiberius

10 kW

Hi fechter,

What more info can you give on the system in the picture? Obviously they have solved the EMC problem with the processors, or maybe its not for a motor application. I don't see why it has to be expensive to do it that way, so knowing more would be useful.

What is the application?

Can you see what supply line filtering is on there?

Mind you, those resistors look as if its designed for nearly 2 A balancing current. Just switching that on and off could upset a processor if the circuit design is careless.

Nick

What more info can you give on the system in the picture? Obviously they have solved the EMC problem with the processors, or maybe its not for a motor application. I don't see why it has to be expensive to do it that way, so knowing more would be useful.

What is the application?

Can you see what supply line filtering is on there?

Mind you, those resistors look as if its designed for nearly 2 A balancing current. Just switching that on and off could upset a processor if the circuit design is careless.

Nick

wrobinson0413

1 kW

.

wrobinson0413

1 kW

.

The transistor level shifter is a current driven system, so it's relatively immune to dv/dt problems. Capacitances are so low compared to data rate that it should also be fairly immune to inter cell inductive spikes (output capacitance of small signal transistor is only around 5pF). In the absolute worst case you can add a small amount of capacitance across the collector resistor to mitigate capacitively coupled noise. However you can approach the problem anyway you like. For a one off system cost isn't very important.

The resetting problem was related to insufficient supply filtering, not the inter CPU communications.

Down regulating the supply voltage for the CPU will solve most of your supply glitch/noise problems (assuming it's done correctly, this was covered in the thread I believe. It also creates a voltage reference for your A/D to work with. It will increase quiescent current however because of the regulator. This may be small enough to be acceptable with a low current regulator.

Besides testing it with a capacitive load you should test it with a motor load, including the freewheeling diodes. The induced voltage spikes will be substantially different in polarity and magnitude.

Yes the concept is certainly workable. I don't know if the people in this thread have working systems yet or not. I have heard of other implementations elsewhere that do work. Read the thread, there may be other useful info I've forgotten that was covered.

Give it a go.

The resetting problem was related to insufficient supply filtering, not the inter CPU communications.

Down regulating the supply voltage for the CPU will solve most of your supply glitch/noise problems (assuming it's done correctly, this was covered in the thread I believe. It also creates a voltage reference for your A/D to work with. It will increase quiescent current however because of the regulator. This may be small enough to be acceptable with a low current regulator.

Besides testing it with a capacitive load you should test it with a motor load, including the freewheeling diodes. The induced voltage spikes will be substantially different in polarity and magnitude.

Yes the concept is certainly workable. I don't know if the people in this thread have working systems yet or not. I have heard of other implementations elsewhere that do work. Read the thread, there may be other useful info I've forgotten that was covered.

Give it a go.

wrobinson0413

1 kW

.

Biff

100 W

I intend to read most of the posts in this thread, but since there are so many pages I will probably miss something important. Is there a summary of the design ideas that are found in this thread? When I designed my own BMS (details below) I found a WIKI was a good place to keep all my deign ideas because it allowed me to edit the deisign in one spot, rather than try and search through pages of revisions and ideas.

To give you an Idea of my background see the text below. If anyone has spesific questions about my BMS, please send me a PM.

-ryan

I made a BMS system for an electric vehicle (solar powered vehicle)

Here are its features:

Monitor up to 48 Series Lithium Cells (approx 200V Peak)

Determine Cell voltage of each cell to within approx 2mv (even in electrically noisy environment) Sampling each cell approx 80 times per second.

Determine Current to within 10mA

Monitor Temperature

Control Battery cooling fans,

Control Main and Precharge Relays (and Solar Array relay)

Over current shutdown, with different set points for Charge and Discharge

Over/under Temperature Shutdown

Over / Under Individual Cell voltage Shutdown

Current Integration for State of Charge Approximation

Charge and Discharge Balancing (can either drain or charge any cell at approx 5A)

CAN interface to monitor/control/configure operation

Here is how it worked:

Cell Protection:

cell protection modules monitored groups of 8 series voltages

Each protection module had an High voltage common mode Differential OP amp On each cell which takes two high voltage inputs and outputs the difference between them with refrence to ground. I believe we used the AD629 op amp (Almost $6 each http://search.digikey.com/scripts/DkSearch/dksus.dll?Detail?name=AD629ANZ-ND)

Each module had an 8 input A/D converter with SPI (http://search.digikey.com/scripts/DkSearch/dksus.dll?Detail?name=MCP3208-BI/P-ND) on board

The module board had a header for a cell balancing Daughterboard.

The Current Temperature protection module board used the Same ADC, but didn't need the op-amps. It used 0-5V temperature sensors and hall effect current sensors that could measure up to 100A

Each protection module board communicated back to the main board over the SPI bus. I communicated to all boards in parallel, so the micro-controller would get cell X from all cell protection boards and a voltage from the current / temperature board at the same time.

The Cell Balance Daughterboard was full of small relays, that could be configured to connect to either the current limited voltage supply, or to a 0.7Ohm resistor.

The Main board had a CAN interface to communicate with other vehicle systems (i.e Driver Display / Battery Balancing system), and all functions of the BMS could be configured/controlled through our telemetry computer connected wirelessly to the CAN bus.

This system was pretty good, but really expensive. The whole setup was around $1400 for parts/printed boards. I think with some design tweaks, and less accurate requiremens the cost could come down to around $200 in parts. For a 24 Series cell system that could be reduced to around $150 probably.

To give you an Idea of my background see the text below. If anyone has spesific questions about my BMS, please send me a PM.

-ryan

I made a BMS system for an electric vehicle (solar powered vehicle)

Here are its features:

Monitor up to 48 Series Lithium Cells (approx 200V Peak)

Determine Cell voltage of each cell to within approx 2mv (even in electrically noisy environment) Sampling each cell approx 80 times per second.

Determine Current to within 10mA

Monitor Temperature

Control Battery cooling fans,

Control Main and Precharge Relays (and Solar Array relay)

Over current shutdown, with different set points for Charge and Discharge

Over/under Temperature Shutdown

Over / Under Individual Cell voltage Shutdown

Current Integration for State of Charge Approximation

Charge and Discharge Balancing (can either drain or charge any cell at approx 5A)

CAN interface to monitor/control/configure operation

Here is how it worked:

Cell Protection:

cell protection modules monitored groups of 8 series voltages

Each protection module had an High voltage common mode Differential OP amp On each cell which takes two high voltage inputs and outputs the difference between them with refrence to ground. I believe we used the AD629 op amp (Almost $6 each http://search.digikey.com/scripts/DkSearch/dksus.dll?Detail?name=AD629ANZ-ND)

Each module had an 8 input A/D converter with SPI (http://search.digikey.com/scripts/DkSearch/dksus.dll?Detail?name=MCP3208-BI/P-ND) on board

The module board had a header for a cell balancing Daughterboard.

The Current Temperature protection module board used the Same ADC, but didn't need the op-amps. It used 0-5V temperature sensors and hall effect current sensors that could measure up to 100A

Each protection module board communicated back to the main board over the SPI bus. I communicated to all boards in parallel, so the micro-controller would get cell X from all cell protection boards and a voltage from the current / temperature board at the same time.

The Cell Balance Daughterboard was full of small relays, that could be configured to connect to either the current limited voltage supply, or to a 0.7Ohm resistor.

The Main board had a CAN interface to communicate with other vehicle systems (i.e Driver Display / Battery Balancing system), and all functions of the BMS could be configured/controlled through our telemetry computer connected wirelessly to the CAN bus.

This system was pretty good, but really expensive. The whole setup was around $1400 for parts/printed boards. I think with some design tweaks, and less accurate requiremens the cost could come down to around $200 in parts. For a 24 Series cell system that could be reduced to around $150 probably.

Tiberius said:Hi fechter,

What more info can you give on the system in the picture? Obviously they have solved the EMC problem with the processors, or maybe its not for a motor application. I don't see why it has to be expensive to do it that way, so knowing more would be useful.

What is the application?

Nick

I can give you a little more information. This was designed as a modular BMS for ThunderSky cells, from 40 to 90 Ah, which is why it has two different terminal spacings. It's completely programmable for voltage setpoints, so can be used for other LFP batteries. All the modules communicate with a master controller; that controller currently has a display for minimal system information, but is obviously extensible. Without the controller, it just functions as the high voltage balancing shunt.

Originally used for motorcycle applications, the picture shown is of a Prius plug-in hybrid conversion of 80 40Ah cells (240 V nominal). I expect it will also see duty in auto and quad conversions as well. It doesn't have to be expensive, but with small volumes it's $20/cell plus $200 for the master. Hopefully costs will come down considerably with higher volumes. It is available if you need it now.

The is also the issue of heat dissipation. Those resistors can get pretty warm, if not hot. I don't have specifics on that right now.

HTH,

Patrick

wrobinson0413

1 kW

.

wrobinson0413

1 kW

.

Biff

100 W

wrobinson0413 said:Ouch! I thinking of economy version myselfMaybe $2 per cell with a $15-$20 master. Edit: I think the per cell cost should be more like $1.50 . I suppose no matter how you look at it, the more cells the more money you will be putting out

Biff said:The whole setup was around $1400 for parts/printed boards.

The Op-Amp alone was $5 per cell.

I think the cheapest approach might be to have 8 cell protection boards that get power from the cells they protect, then optically isolate the communication between the main board and the cell protection boards.

One potential problem with that design is stand by current draw. I.E. with each board having its own (cheap) DC/DC converter you would have a few mili-amps being drawn all the time, which is not good if you leave your battery pack sitting for a couple months. You could put a relay or Fet or relay on each board to solve that problem, but then you add more complexity / cost to the over all system. That is why its good to post these kind of ideas in a forum like this, and get feedback on designs.

Similar threads

- Replies

- 3

- Views

- 1,117

- Replies

- 8

- Views

- 1,328

- Replies

- 0

- Views

- 3,136

- Replies

- 8

- Views

- 2,193