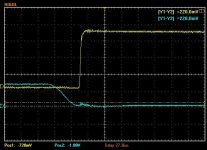

as dead time increases, the AC output voltage distortion increases and is no longer sinusoidally shaped perfect.. so the peak is not there any more and so the current decreases. as a rule of thumb, your dead time to switching period ratio should not exceed 5%, otherwise way too much distortion and your system suffers to a point where a new design would be better... or ask Lewbowski about his deadtime compensation software version.

dead time works like this. it is always safe to turn a mosfet OFF instantly.. but it is not necessarily safe to turn a mosfet ON. if you want to turn a mosfet ON you must be absolutely SURE that the other adjacent mosfet is OFF. since your gate driver makes no measured determination of when it is actually off, you have to guess.. i.e. by applying an arbitrary delay of fixed duration, "deadtime", weither or not that time was way too much or just enough.. always the same value, not dynamic.

we can make an educated guess at what an appropriate worse case dead time should be. to do this you must be able to understand where all your signal propegation delays are. i.e. i want to turn Mosfet OFF but i know this does not happen instantly. how long does it take for this OFF signal to leave the digital controller and actually see a mosfet drain/source voltage increase to DC bus voltage? where are the major delays? digital to gate driver is negligable. at input of gate driver is usually some sort of isolation (i don't know your design, have not seen schematic) and this isolation, like an opto-coupler, usually has some delay time. if you are using an IRF gate driver chip then read the datasheet to see what its MAXIMUM propegation time is to turn a mosfet OFF. the next delay will be in the boost stage if you have one. the next is in the mosfet fall time (see datasheet). the final is fall time delay of mosfet (also see datasheet). look for maximum values (worse casae).

if the max is not listed, only typical, then you have to calculate the fall time & delay by reading the curves of the datasheet. i can help you more here if you need it. take this total propegation delay time and that is your dead time. i realize that the ON command of mosfet also has delay, theoretically the fastest time this can turn on could be subtracted from the previous calculation to get a more fine tuned dead time but i don't do this, i like to ignore the turn ON time factor and think of it as added safety margin. now check that deadtime with respect to your switching period.. less than 5% good. greater than 5%? lower your switching frequency or change your gate driver design or mosfet selection.

gate resistors.. having one or two low resistance and then a third as 20 ohms just means that the 20 ohm resistor will take the bulk of the power losses and should be sized such. to me it does not make any sense at all to do it this way, the resistors should all be same value. only time you would have values significanly different is if you had one resistor (or group of series resistors) driving ALL parallel mosfets and then a second single gate resistor of much lower value PER mosfet.

that is 20 ohm each per parallel mosfet? that is huge... look at your mosfet datasheet and find the curve that describes switching time vs. gate resistance. on the X-axis will be gate resistor.. if your total series gate resistance is greater than the highest value on that X-axis then it is too high and your mosfet will underperform (switching times too long for mosfet die level design). so you will have higher than necessary swithcing losses and stress mosfet due to length of time in linear region. if this becomes a problem solution is to lower gate resistor or if you can not (due to some not ideal problem in system design) then lower the switching frequency. lowering temperature will have little effect here as this has little to do with mosfet switching losses.

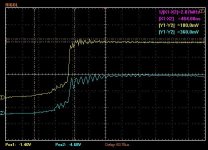

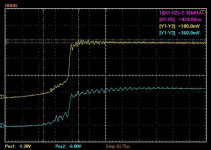

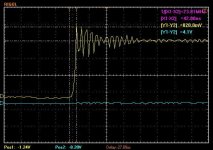

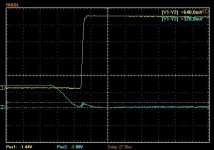

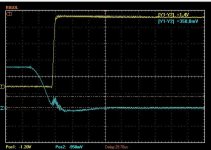

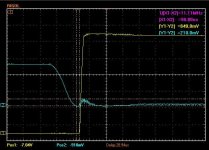

#1 cause of ringing is power bridge assembly.. clean layout, laminated bus bar, quality parts.

always some ringing is normal. typical thing to do is increase gate resistance until you can find a balance between decreased ringing and mosfet power dissipation. you can only increase the gate resistance so far though (see further below).

another, less likely, cause is:

one thing about your design is that your mosfet heatsink also carries phase current. that is unusual.. never seen that before. not too big a deal in of itself, but this phase output heatsink also has a switching voltage on it. your chassis will have some other voltage, probably 0V. between the two is a piece of kapton tape. so this is like a capacitor.. two plates of different potential with a dielectric between them, ya? and the plates are large area just like capacitors appreciate. on top of that is one of the plates not only has a potential, but it is a changing potential.. from bus voltage to zero, and repeat 40,000 times a second. this will inject a current.. i = C*dv/dt. if this capacitor were to be of such a value as to resonate with an inductance that is elsewhere in the network that would cause ringing. the mosfet switching goes through a HUGE frequency spectrum so it is quite likely to find a resonance if there is such an LC network..

i would need to know more about your design in order to help with the ringing issue. or you can try solving by trial and error different tests.

for Mosfet switching losses & junction temperature my preferred reference is "MOSFET Power Losses Calculation Using the Data-Sheet Parameters" by infineon. all the manufacturers have their own formula for mosfet switching losses .. unfortuantely. it is not like IGBT where datasheet gives switching losses in convenient single unit of joule. no.. for mosfet it is all timing waveform extrapolation and so weird formula

i have worked out fully the math for this if you want but it is basically just the infineon app note with some modifications i made. i do not linearize the mosfet performance as infineon suggests, instead i take the datasheet curve as it is, with a shape.. not a straight line and curve fit. linearizing is OK if your operation never changes.. like a DC/DC converter with a fixed load. but a sinusoidal current output goes through 0amps to max amps in ONE cycle! and it changes all the time depending how the driver presses the gas peddle.. also, for junction temperature it is important to iterate which infineon does not do. that is, use their app note to calculate the power dissipation (but use curve fit technique instead of linearization) then calculate what the junction temperature will be. then, with that new junction temperature.. re-calculate the power dissipation, and repeat until successive iterations have less than 2 degC between them. then your result is much more accurate & now actually useful for power bridge sizing.

$0.02