Ok today I got to some loaded testing. IT RUNS AND NO BLOW UPS SO FAR  Knowing this is a current throttle (torque throttle) I set the max phase amps to 100 amps thinking if the wires brake or short on the tps it should still survive. I never went full throttle so far about 40% is the most I have give it. I mostly spent time at 0-20% throttle so get scope measurements.

Knowing this is a current throttle (torque throttle) I set the max phase amps to 100 amps thinking if the wires brake or short on the tps it should still survive. I never went full throttle so far about 40% is the most I have give it. I mostly spent time at 0-20% throttle so get scope measurements.

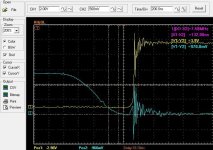

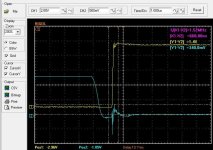

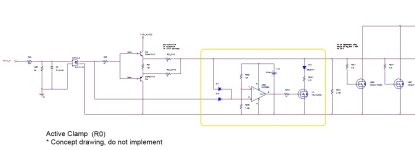

Here is what I found under load my dead time was to short.... Well kind of. I found I'm still getting the low gate pulling up when the hi side turns on. I upped the dead time and it was a lot better but the fix is a different fet driver or some more fancy work with resistors.

Here is what I think. If I turn the high side on slower then the low gate will not have as hard of an issue staying off. If I set up the low side to turn off with less resistance it should hold it off better. So between working with these two I should be able to get it sorted.

Let me know if you guys have any other tricks.

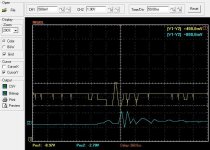

I did notice some of the overshoot as well which I think is like I had before and had to solve with caps and diodes on the rails but I will sort the gate resistors first then look at that as I up the amps. So far the over shoot is only to 105v on a 83.5v pack and the fets are rated to 150v this might be a problem as I up the voltage but I think I can spend the time setting most of it up at 84v (20s) first.

I had to quit for the day because I tried to hook a probe ground to the phase wire when the other probe was grounded to the - lol I know better but thought maybe they didn't connect the grounds in this scope... Apparently the ground clips form Rigol have fusible wire in them I have some more on order but for tomorrow I will try some repairs to get going. I did a self calibration and I think the scope is ok....

Apparently the ground clips form Rigol have fusible wire in them I have some more on order but for tomorrow I will try some repairs to get going. I did a self calibration and I think the scope is ok....

Here is what I found under load my dead time was to short.... Well kind of. I found I'm still getting the low gate pulling up when the hi side turns on. I upped the dead time and it was a lot better but the fix is a different fet driver or some more fancy work with resistors.

Here is what I think. If I turn the high side on slower then the low gate will not have as hard of an issue staying off. If I set up the low side to turn off with less resistance it should hold it off better. So between working with these two I should be able to get it sorted.

Let me know if you guys have any other tricks.

I did notice some of the overshoot as well which I think is like I had before and had to solve with caps and diodes on the rails but I will sort the gate resistors first then look at that as I up the amps. So far the over shoot is only to 105v on a 83.5v pack and the fets are rated to 150v this might be a problem as I up the voltage but I think I can spend the time setting most of it up at 84v (20s) first.

I had to quit for the day because I tried to hook a probe ground to the phase wire when the other probe was grounded to the - lol I know better but thought maybe they didn't connect the grounds in this scope...