I would think its best if you can take a different mosfet and pace the numbers in from it to demonstrate.

we are talking about math, concept and philosophy as the elements that make up the deadtime value. math because calculate the difference which is just a subtraction so fairly easy. Concept because we want worse case off time minus fastest ON time since we need to ensure deadtime delay is always enough (i.e. over temperature, aging, overload current, everything). Philosophy, we put fault protection as high priority when inverter power is high because usually the costs are high so worth protecting and also if the application would benefit from it which i think is the case for electric vehicles (except for bicycles which is less important if there is a mosfet blowup because you can always peddle home).

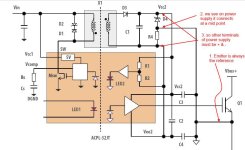

you haven't posted a schematic yet, so i will make some assumptions. i assume you are using lewbowski brain board and connecting it to gate driver board and your power mosfet is IRFB4110 (4 in parallel). now we have to identify all the delays.

1. starting at brain board, what is the delay difference between the PWM ON command and PWM OFF command (we start by assuming no deadtime). well the brain board is so fast probably the delay is less than 10ns, so we call this negligible.

delta_brain = 0s

2. between microcontroller on brain board and the gate driver logic input, what circuitry is there? i assume that you have only a resistor in between, specifically no low pass filter, no circuit chips doing something, nothing. so there is virtually no delay between the time it takes to turn one mosfet OFF vs. time it takes to turn ON.

delta_PWM = 0s.

3. then PWM signal reaches input of gate drive IC, part number ACPL-32JT and we finally find our first elements of delay. for example, if the lower mosfet gate drive IC were asked to turn OFF, what is the worse case time it would take? on page 12 of datasheet we see delay to turn OFF worse case is 250ns and fastest to turn ON is 50ns. so delta_gateIC = 200ns. but look carefully, these values are given at 25decC and also there is a line just below talking about pulse width distortion (PWD) and deadtime distortion (DTD).

3a. effect of temperature. on datasheeet pg 12 it says on right hand side to look at figure 17. scroll down the sheets we see that propagation delay is affected by temperature, but not too much. that is, at any one temperature, the curves for delay ON and delay OFF change with about the same inflection which means although the ON time or the OFF time changes quite a bit (50%?) the DIFFERENCE between them does not change too much, at most looks like 50ns. so we can update our equation:

delta_gateIC = 200ns + temperature_affect = 250ns

3b. i think PWD means that the gate drive IC is not always accurate, that is when it receives a 1400ns PWM_ON command from brain board it may output anything between 1360ns and 1540ns. so we re-work the numbers by assuming worse case. if gate drive OFF command takes worse case 250ns then the distortion could add another 140ns to this. if gate drive ON command is as fast as 50ns then we could subtract 40ns from this due to distortion.. so the distortion delta is: 140ns - 10ns = 130ns, and we update our equations:

delta_gateIC = 200ns + temperature_affect + Pwdistortion_affect = 200ns + 50ns + 130ns = 380ns.

3c. i think deadtime distortion means that chip-to-chip there is variation. if lower gate drive receives 1400ns pulse width at same time as upper gate drive then it is possible that between the two there is possible a difference of -160ns to +60ns. note that this datsheet parameter is already given in differential units (delay high minus delay low). but what we are really calculating is delay low minus delay high, so we take the -160ns and consider it as +160ns and add this to our equation:

delta_gateIC = 200ns + temperature_affect + PWdistortion_affect + DTdistortion_affect = 200ns + 50ns + 130ns + 160ns

delta_gateIC = 540ns

interesting how the propegation delay of this gate drive just went from 250ns to 540ns eh?

4. next we consider the circuitry between gate drive IC and power switch. this depends a lot on your need of a boost stage or not. let's assume it does. what is the longest time it takes to propegate an OFF signal vs. shortest time to propegate an ON signal? i'm running out of time to answer this by reading datasheets and stuff, so i'm just going to assume the answer is 100ns (transistors tend to be fairly fast).

delta_boost = 100ns (not verified)

5. finally.. the power switch. how long does it take for mosfet to turn OFF vs. how fast to turn ON? so for turn OFF we see off delay of typical 78ns + fall time of 88ns for total of 166ns. similar for fast turn ON is 25ns + 67ns = 92ns. these numbers are at 25degC and also note these are typical time (datasheet does not specify worse case for some reason) so for sure we have to look at datasheet curves to see if we can find affect of temperature. except this datasheet does not have any! ugg.. we have to make a WAG (wild ass guess). so if the typical room temperature delta difference is 166ns - 92ns = 74ns, let's assume the variation on that is 50% so delta_IRFB4110 = 110ns. that is for ONE mosfet, but we assume 4 in parallel. what is the variation between MOSFETs? i don't know and it is not specified on datasheet, but it is a controlled element because you will make an effort to match the mosfets prior to installation for current sharing reasons. let's say the difference is small, around 20%. so

delta_IRFB4110 = 110ns + 110*0.2 = 130ns.

now we can add up our deadtime and multiply result by safety margine of 1.2 to get total deadtime:

deadtime = (delta_brain + delta_PWM + delta_gateIC + delta_boost + delta_IRFB4110)*1.2 = 770ns * 1.2 = 924ns.

which is JUST less than the desired 1us limit (see previous post).. rejoice!

now you can post the math for the leaf inverter result