strantor

100 W

mouser. only one left. I would have bought both but I'm not rich enough. gotta be super careful with the one I got

Yes they are basically a bunch of FETs in one package. The difference is that when paralleling discretes, there are a lot more variables. different Ls, Cs, and Rs in the individual packages and in the circuit. in these modules they go straight to the source, bypass all the middlemen and parallel the devices at the silicon level which (should, we will see) eliminate all parallel-FET-induced problems currently being realized in the commercial controllers. Theoretically all the FETs in the module should always share the load equally. The only reason I can see for the big guys paralleling 30+ FETs on a board is to cut cost. For a guy like me making a one-off controller, I can't justify going through several revisions of circuit board until I stumble on one that fits (and probably end up spending more money in the end and definately more time) when this pre-packeaged solution exists.megacycle said:Thanks strantor.

After looking at previous posts about this type of beastie, excuse my niavity, did'nt realise they are'nt monolithic internally just multiple fet chips, understandable if manafacturer makes millions of 100A fets chips. Can see now why the professionals might want to parallel discretes

These modules might be good for additional cooling mods i've been obsessing about,if lid comes off them.

Can't understand massive heatsinks if a fet is going to be hammered for a few minute bursts, would think snap freezing might help, read somewhere fets take to freezing improves parameters massively where IGBT'S don't take to it.

strantor said:Hi, thanks for that lengthy reply. I'm not yet schooled enough to address most of it; I am reading however, at a torturous rate. maybe in a couple of weeks I will be able to carry on a decent conversation on the topic. one thing I would like ask, regarding this:

this seems to be disagreement with moose's last document he linked to (the way I interpret it). If you have a look in that doc, section III (b) (i):Electroglide said:Fets do share reasonably good if they share a common electrically connection point and share a common heat spreader. They are positive temperature coefficient devices...ie the Rdson goes up with temperature which means that parallel mosfets will reach an current equilibrium point that is dependent on the die temperature and the circuit impedance between the devices.

For two

devices from the same date code, the predicted 18% maximum

unbalance is reduced to 14% allowing for temperature

compensation. For N large and without screening, temperature

compensation reduces the predicted maximum unbalance from

85% to 56%. Note that these reductions assume a common

ambient temperature. If a common heatsink is used, the

reductions will not be as large (refer to condition (b) above).

For simplified heatsink design, see reference 10.

and later on in section III (d) (vi)

Seems to me, by using a common heat sink, you are "locking them in" to a common temperature, which undermines their intrinsic tendency to share the load.Current unbalance due to ON resistance mismatch is reduced by allowing different junction temperatures. This reduction is

maximized for a large number of devices.

I believe this paper was written in 1981, so things may have changed. Also, this paper seems very "theoretical", and I don't know whether to take the things is says literally, or if things in real life might be different. So, What say you? is it better to have separate heat sinks or common heat sink?

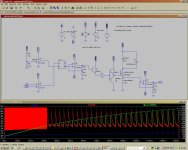

strantor said:(...) and creating a inverted copy of it to switch 2 darlington transistors to create (...)

Great input, much appreciated!bigmoose said:There are a number of things that may help:

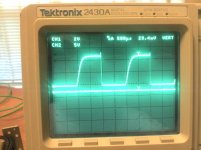

- The NTE534 is open collector design and is a little slow, about 3 or 4x what I would like to see. It's output impedance is too high with the open collector for fast switching.

The totem pole needs about a 4.7uF or more tantalum bypassing it, not a 0.1uF

There needs to be about 1 or 2 ohms in the gate of the BIG FETs to damp oscillations once you get them to switch fast.

Basically the NET534 is not a FET driver. I like to roll my own totem pole (emitter follower) current amplifiers afer a IR2113S

Zetex makes some great transistors for use in the emitter follower. We want speed and pulse robustness. I couldn't find switching characteristics on the TIP42, so you may have to measure it with your scope. The NTE2343 is a darlington! Slow, too slow...

Your driver has DC current capability, but seems to be lacking in speed and pulse power capability. Basically not the parts I would spec for driving a brick.

Yes, it is probable that it never turns off. I have seen driver circuits that only use a NPN with a pullup resistor. my PNP is probably just acting as a pullup resistor if it is in fact not switching.Njay said:There's something wrong with your schematics, I don't see how the TIP42 turns off, since it's a PNP and you're driving it with GND or 5V while it's emitter is at 12V. But let's assume the vcomp is powered by 12V and not 5V as in your schematics.

The osc figure shows that it's the charging of the gate that is slow. TIP42 datasheet shows typical gain of 50 @ 2A, that means it needs at least 2 / 50 = 40mA base current. The 2.2K base resistor only allows a max of ~5mA into the base.

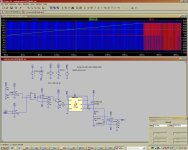

Yes I am going to scrap this driver circuit and go with a real driver IC. I like the High current buffer circuit you linked to, thanks for that! While looking for driver ICs before, I ran across the FAN3122 (http://www.fairchildsemi.com/ds/FA/FAN3121C.pdf). It claims 7A peak output from the IC itself, with no buffer circuit. Also the IDX_630 (http://www.mouser.com/ProductDetail/Clare/IXDD630CI/?qs=sGAEpiMZZMvQcoNRkxSQkn6jLm8xbgsJXhV6HaofQC4= - For some reason the datasheet has disappeared since last week; I should have printed it while it was still available) which claims 30A output. Have you used a high output driver IC like this before? Would you think that it can match the performance of the buffer circuit?bigmoose said:Njay is right, I didn't even notice the voltages. If you want the short path to success. Drop in a IR 211x series FET driver, and then buffer it with what you learn on the attached app note. I also added the IR app note for buffering with FETs, it has some very, very nice demonstrated switching waveforms!

Good luck!

DOH! Yes I did indeed erroneously think that the TIP42 was a darlington, hence the large gate resistor and minimal current.Njay said:I guess that explains the circuit's lousy performance, strantor thought he was dealing with 2 darlington and the resulting top drive ended up too weak.

Njay said:You know, I was looking at the current source circuit with an ampop and thinking if we could get an ampop plus a transistorized power output to "force" a bunch of FETs to equally share current. We could loosely measure the current across the FET and compensate with temperature to avoid using the shunt. We could just then toss it FETs without matching, and I guess that would also forgive some layout "sloppiness". The reference for the ampops would be square wave with controlled raise and fall times, which would control the FETs to turn ON/OFF in a "synchronized" way. Could we make switch under 1us this way without expensive hardware and would it be worth it?

update: humm, it's an inductive load... not sure if the switching phase can be made without an external shunt. back to the books...