thorlancaster328

100 W

- Joined

- May 25, 2018

- Messages

- 198

It was with the old ones, but with the new current sensors, that's not much of an issue anymore. I have the overcurrent detect pin routed to an interrupt pin on the Teensy, and the overcurrent detection interrupt will have higher priority than everything, including the FOC interrupt. The <~1us interrupt latency isn't going to make much of a difference when you factor in the current sensor response time + filter rise time of around 3 us. Won't save the FETs from a hard short (almost nothing will), but it will protect from pretty much everything else.No hardware over current

These things can kill people. Having the freedom to fettle by running 10 lines of terminal in Linux is dangerous... Any newb can change the current limits, voltage limits in a few minutes, and then face plant their onewheel or whatever when it burns.

That's a good point, but I'll mitigate it by slapping a "warranty void" sticker over the Teensy and its USB port in the final product. The code will also include a license that explicitly disclaims any warranty, along with a warning that modification / flashing of the code may cause bad things to happen, including serious injury or death.

I'll also have the WDT set up so that if the FOC interrupt fails to fire within 1.5x the expected interval, all pins will go hi-z and pullup resistors will turn all FETs off. When the chip resets from the WDT, it will refuse to even turn on a FET until power is cycled and blink an error code on the LED. This will make development somewhat safer, although I'll still be using a low-value fuse (30ish battery amps) until I'm sure it's bulletproof.

Arduino programs ("sketches") can be split up into files that handle different parts of the program. Currently, I have one for look-up tables, one for vector stuff, one for FOC and low level stuff, and one for main functions (incl. Serial communication etc).

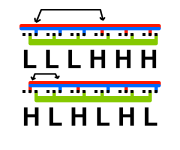

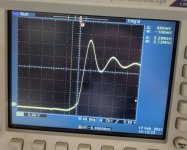

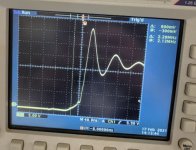

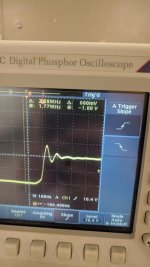

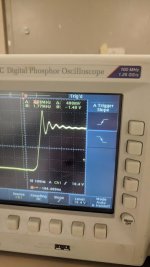

There's still a good bit of switching noise in the readout due to the current varying through the motor's inductance. I found I get better results without synchronized ADC, I have the ADC set up for max speed and have it free-run across the three phase current sense lines. I typically get around 10 ADC readings per PWM cycle per pin, and by throwing away the top and bottom quartile and average the rest. The noise in the readings drops by around 4x this way.The isolated phase sensors make synch with pwm optional... Which makes the code much more portable.

P.S. JLCPCB just finished producing V2, it should be here in around 5 days. Will give me some time to get ahead in my classes so I can spend a few days straight on this next weekend.