hardym

100 W

Very impressed with Jeremys ongoing Simple BLDC project at http://endless-sphere.com/forums/viewtopic.php?f=2&t=23350

However, I think that there is a better brain for a controller than a MC33033. I believe that all of the functionality can be better implemented in a flexible CPU architecture rather than burned into a fixed silicon implementation.

The features that could be better implemented in SW are

- soft start

- adjustable current limit

- hall event filtering

- output data stream and data logging

- timing tuning

There have been several threads that have postulated how this could work, instead of commenting, I built one. I used a PIC16F690. I utilized the internal PWM for the throttle control, a comparator for the current limit (~10uS response), and the pin interrupt architecture for the hall sensor inputs. The rest is pretty straight forward PIC stuff.

The software and hardware will be updated and posted into this top topic posting. I've yet to go for a test drive -- a test ride is worth a thousand calculations.

Here is a video of the brain in action. It is hacked into a 12 FET controller (not an infineon), and testing with a bench power supply.

My hope is that this can one day be used with Jeremys awesome simple brawn project:

Video:

[youtube]kOyKSl5j4UQ[/youtube]

Software is written in Microchip's Free C (Hi-Tech C), using the standard libraries.

(I had to post in PDF as .c and .txt attachments are not allowed

Verison 1.0 Initial release

Version 1.2 improved soft start, improved display, speedomoter gauge.

View attachment main-brain.1.2.pdf

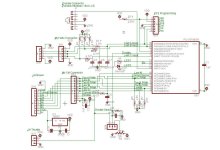

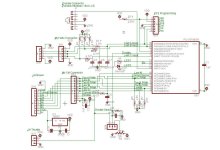

Schematic:

V1.1 changes include Hall filtering and extra headers for Jeremys brawn.

V1.2 adds more filtering needed on throttle inputs and current sensor inputs

Mark.

As always, suggestions encouraged!

The Tin Man,

However, I think that there is a better brain for a controller than a MC33033. I believe that all of the functionality can be better implemented in a flexible CPU architecture rather than burned into a fixed silicon implementation.

The features that could be better implemented in SW are

- soft start

- adjustable current limit

- hall event filtering

- output data stream and data logging

- timing tuning

There have been several threads that have postulated how this could work, instead of commenting, I built one. I used a PIC16F690. I utilized the internal PWM for the throttle control, a comparator for the current limit (~10uS response), and the pin interrupt architecture for the hall sensor inputs. The rest is pretty straight forward PIC stuff.

The software and hardware will be updated and posted into this top topic posting. I've yet to go for a test drive -- a test ride is worth a thousand calculations.

Here is a video of the brain in action. It is hacked into a 12 FET controller (not an infineon), and testing with a bench power supply.

My hope is that this can one day be used with Jeremys awesome simple brawn project:

Video:

[youtube]kOyKSl5j4UQ[/youtube]

Software is written in Microchip's Free C (Hi-Tech C), using the standard libraries.

(I had to post in PDF as .c and .txt attachments are not allowed

Verison 1.0 Initial release

Version 1.2 improved soft start, improved display, speedomoter gauge.

View attachment main-brain.1.2.pdf

Schematic:

V1.1 changes include Hall filtering and extra headers for Jeremys brawn.

V1.2 adds more filtering needed on throttle inputs and current sensor inputs

Mark.

As always, suggestions encouraged!

The Tin Man,