Lebowski

10 MW

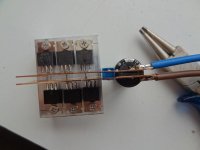

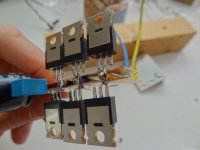

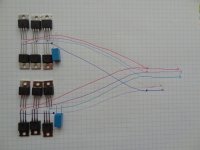

I;ve been walking around with an alternative method of building an output stage for some time now. After all the programming

I did for the controller IC I wanted to do some old fashioned soldering so yesterday I decided to implement my output stage

idea. Before I start with the idea behind it and the explanation, first a teaser picture of the result

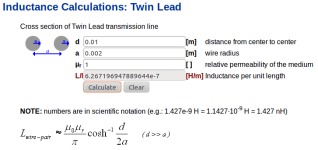

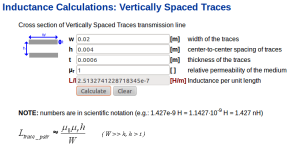

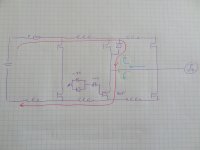

The construction is a result of the learnings of my 'output stage musings' thread. Which can be summarised to "limit the power

supply inductances as much as possible".

The explanaition assumes the use of center aligned PWM, but I think it's also applicable to the standard china controller type PWM.

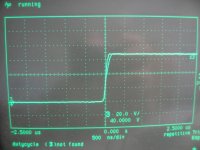

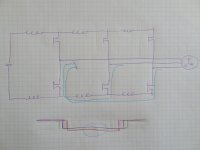

The bottom of the picture shows the center aligned output stage voltages. In the picture they start of 'low', then the 3 signals transition

to 'high' and back again. The different transition moments is what actually provides the power to the motor. But a large part of the

time all three output stage signals are either 'low' or 'high'. The schematic in the picture shows how the motor currents effectively

run around in a circle through the high side transistors and the parasitic power line inductances. The motor is assumed to have a

relatively high inductance, meaning the motor currents are constant (but yes, they have a triangular shape but the amplitude of the

triangle is low w.r.t. the average motor current).

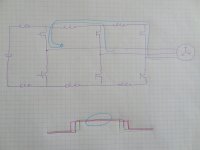

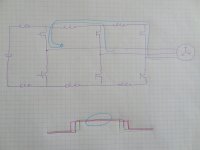

This picture shows the other half of the PWM cycle where all low side transistors are switched on. Note that the motor currents

have not really changed, they still flow in the same direction but now they all take the path through the low side transistors and

the parasitic inductances of the negative power line.

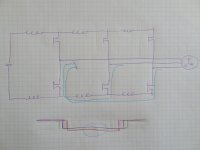

It is important to realise that first all the currents were going through the positive power line inductances, and now they are flowing

through the negative power line inductances. An inductor is an energy storage element, just like a capacitor. After the motor currents

stopped flowing in the positive power line inductances, these inductances 'dumped' their energy into the FETs, in the form of a

large voltage spike. And similarly for the negative power line inductances, when the currents are transferred to the positive power line the

inductor's energy will be dumped in the FETs in the form of a voltage spike.

The inductances that matter are the ones inbetween the three output stages, as these carry the full motor currents one half of

the cycle and no current at all the other part of the cycle. The motor current, except for the triangular ripple, stays constant. And

in the case of a sine wave controller, also the battery current is constant. The only real switching currents are between the three

output stages and the power line caps. So an output stage should keep these inductors to a minimum.

I did for the controller IC I wanted to do some old fashioned soldering so yesterday I decided to implement my output stage

idea. Before I start with the idea behind it and the explanation, first a teaser picture of the result

The construction is a result of the learnings of my 'output stage musings' thread. Which can be summarised to "limit the power

supply inductances as much as possible".

The explanaition assumes the use of center aligned PWM, but I think it's also applicable to the standard china controller type PWM.

The bottom of the picture shows the center aligned output stage voltages. In the picture they start of 'low', then the 3 signals transition

to 'high' and back again. The different transition moments is what actually provides the power to the motor. But a large part of the

time all three output stage signals are either 'low' or 'high'. The schematic in the picture shows how the motor currents effectively

run around in a circle through the high side transistors and the parasitic power line inductances. The motor is assumed to have a

relatively high inductance, meaning the motor currents are constant (but yes, they have a triangular shape but the amplitude of the

triangle is low w.r.t. the average motor current).

This picture shows the other half of the PWM cycle where all low side transistors are switched on. Note that the motor currents

have not really changed, they still flow in the same direction but now they all take the path through the low side transistors and

the parasitic inductances of the negative power line.

It is important to realise that first all the currents were going through the positive power line inductances, and now they are flowing

through the negative power line inductances. An inductor is an energy storage element, just like a capacitor. After the motor currents

stopped flowing in the positive power line inductances, these inductances 'dumped' their energy into the FETs, in the form of a

large voltage spike. And similarly for the negative power line inductances, when the currents are transferred to the positive power line the

inductor's energy will be dumped in the FETs in the form of a voltage spike.

The inductances that matter are the ones inbetween the three output stages, as these carry the full motor currents one half of

the cycle and no current at all the other part of the cycle. The motor current, except for the triangular ripple, stays constant. And

in the case of a sine wave controller, also the battery current is constant. The only real switching currents are between the three

output stages and the power line caps. So an output stage should keep these inductors to a minimum.