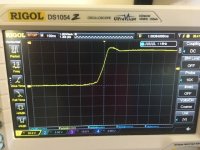

For a couple of last measurements I didn’t use this spring wire to shorten ground distance. At next measurement I will. Noticed that mechanical quality of rigol probes shipped with scope is not very good as after some time ground clamp twisted. Their differential probe is expensier than whole unit. But in a couple weeks I will have access to some far better equipment and repeat measurements. I am not sure if my gate driver with quick and dirty layout can have big influence on overshoot. But for now on this phase of testing this overshoot of 30% looks acceptable as there is a lot of room for reaching maximum Vds from fet specs.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

low inductance output stage contruction

- Thread starter Lebowski

- Start date

zombiess

10 MW

bdj said:I am not sure if my gate driver with quick and dirty layout can have big influence on overshoot.

Gate driver design is THE MOST IMPORTANT PART of a successful build. There are several rules to follow, the hard part is obeying them.

You might find some of the info in this thread about one of my previous builds useful.

https://endless-sphere.com/forums/viewtopic.php?f=30&t=58341

I used this probe config. All test below are done with 60V 33A and 10nF on each fet GS as concluded that with 47nF on lower fet doesn’t get much.

Still same overshoot.

Check with another probe and this time Vds of high fet. Alsmost same overshoot and graphs, timebases are different so on same time base pretty same signal.

View attachment 4

Low side fet turn on.

Low side fet turn off.

Some noise on Vgs of high fet. Do I need to wory about this? Think that good layout would suppress this oscillation.

Next I will look for zombiess gate driver design and lebowski driver design and try to do “good” layout.

Still same overshoot.

Check with another probe and this time Vds of high fet. Alsmost same overshoot and graphs, timebases are different so on same time base pretty same signal.

View attachment 4

Low side fet turn on.

Low side fet turn off.

Some noise on Vgs of high fet. Do I need to wory about this? Think that good layout would suppress this oscillation.

Next I will look for zombiess gate driver design and lebowski driver design and try to do “good” layout.

Attachments

On your last waveforms the ringing looks like an amplitude modulated signal, that is 2 frequencies added. It suggests you have 2 oscillating loops. I've seen similar between Vds of parallel FETs. Do you also have them parallelled either on low or high side? If not, the other loop may be either the gate driver or a probe-effect.

On the other hand, on the waveform on the previous page where you measured the diff, the S-waveform (yellow, with tip and GND shorted) is flat, so I don't see any probe issue there, but the common mode noise is low on that node because it is the DCbus. Try to repeat it on the output signal.

On the other hand, on the waveform on the previous page where you measured the diff, the S-waveform (yellow, with tip and GND shorted) is flat, so I don't see any probe issue there, but the common mode noise is low on that node because it is the DCbus. Try to repeat it on the output signal.

Yes agree. I don’t have parralled fets nither low or high side. But on same dc bus I have another half bridge with two mosfets that I don’t drive at the moment. Their gates are floating, D of high fet connected to +, S of low fet to - , D-S together. That is all concering connections. This leg is planed to be driven as soon as get good waveforms from first leg.

Okey you are suggesting to do diff measurements on Vds of higher fet? GND from both probes on S of lower fet and tips from 2 probes one on common node D-S and other on D of high fet ?

Okey you are suggesting to do diff measurements on Vds of higher fet? GND from both probes on S of lower fet and tips from 2 probes one on common node D-S and other on D of high fet ?

bdj said:Okey you are suggesting to do diff measurements on Vds of higher fet? GND from both probes on S of lower fet and tips from 2 probes one on common node D-S and other on D of high fet ?

Not exactly, I just suggest to connect one probe tip and GND together, and connect it with a single wire (a few cm long) to the output signal (common node D-S). The single wire takes any induced voltage out of the picture. If anything is seen on the display, that is common mode problem.

But do it only if your power supply is isolated from the oscilloscope GND, e.g. your whole circuit is powered from battery and nothing is connected to the wall power or the protective earth. Otherwise this measurement would short the power supply to the earth and could kill the oscilloscope or the circuit. (there is no such issue with a diff probe.) But I think you know it because you already have the high side Vgs and Vds measured.

Concerning the floating gates, it is better to short them to the source pins, anyway.

Here is test as you suggested.

So it is small voltage in probe.

Next I remowed cap from lower fet GS and get same results concerning overshoot Vds.

So decided to check one thing. I am using transformer power supply with diodes and caps about 25000uF unregullated. So without load after caps is 80V dc and when load it with resostor and have about 30A and voltage is 60V dc. So difference is 20 V which exactly matches as “overshoot” peak. So I think this could be isssue with overshoot.

So it is small voltage in probe.

Next I remowed cap from lower fet GS and get same results concerning overshoot Vds.

So decided to check one thing. I am using transformer power supply with diodes and caps about 25000uF unregullated. So without load after caps is 80V dc and when load it with resostor and have about 30A and voltage is 60V dc. So difference is 20 V which exactly matches as “overshoot” peak. So I think this could be isssue with overshoot.

OK, so there is no big issue with the probe and the scope, the oscillation is real.

Shaman's older board had a very similar ringing at low voltage:

https://endless-sphere.com/forums/viewtopic.php?f=7&t=97699&start=125#p1445800

His solution was adding 4.7uF caps on the DCbus on every half-bride (if I understand correctly) and snubbers with 4.7nF capacitors on the outputs. The 4.7uF electrolytic cap also works as snubber in his config, because of its large ESR. He also added the snubbers on his newer designs, as can be seen on the photos.

In any case I think that oscillation is inherent without damping, because Coss is the capacitor of an undamped LC loop, and at turn-on the diode reverse recovery (of the other FET) is a fast transient that initiates he ringing.

You could also increase the gate turn-on resistor even more to make the Vgs rise time slower, because that reduces the peak reverse recovery current (together with the added Cgs), and then the kick from RR is smaller. On your "Low side fet turn on" photo (isn't it the high side if the load is between the output and the GND?) the rise time from start to the end of miller-plateau is about 600ns, try to change it to 1-1.5us with a 50-100ohm turn-on resistor, and keep the 10nF Cgs also at the FET. But it increases the current transition time and the switching loss. Shorter gate driver wires may also help, because generally having the gate drivers on the same board with the FETs or connected with short board-to-board connectors are better than the twisted pair because of the smaller gate driver loop inductance. The gate driver wire above the FET is in inductive coupling with the drain-source current, if you move the wire in any direction, you may see some change on the waveforms.

I think it's not the power supply, that would oscillate at a much lower frequency, but 25000uF is large enough to keep the DCbus voltage even for a millisec (depends on the load current), so if you can program a double pulse test on your controller instead of driving the load for a longer time, that would significantly limit the voltage sag.

Shaman's older board had a very similar ringing at low voltage:

https://endless-sphere.com/forums/viewtopic.php?f=7&t=97699&start=125#p1445800

His solution was adding 4.7uF caps on the DCbus on every half-bride (if I understand correctly) and snubbers with 4.7nF capacitors on the outputs. The 4.7uF electrolytic cap also works as snubber in his config, because of its large ESR. He also added the snubbers on his newer designs, as can be seen on the photos.

In any case I think that oscillation is inherent without damping, because Coss is the capacitor of an undamped LC loop, and at turn-on the diode reverse recovery (of the other FET) is a fast transient that initiates he ringing.

You could also increase the gate turn-on resistor even more to make the Vgs rise time slower, because that reduces the peak reverse recovery current (together with the added Cgs), and then the kick from RR is smaller. On your "Low side fet turn on" photo (isn't it the high side if the load is between the output and the GND?) the rise time from start to the end of miller-plateau is about 600ns, try to change it to 1-1.5us with a 50-100ohm turn-on resistor, and keep the 10nF Cgs also at the FET. But it increases the current transition time and the switching loss. Shorter gate driver wires may also help, because generally having the gate drivers on the same board with the FETs or connected with short board-to-board connectors are better than the twisted pair because of the smaller gate driver loop inductance. The gate driver wire above the FET is in inductive coupling with the drain-source current, if you move the wire in any direction, you may see some change on the waveforms.

I think it's not the power supply, that would oscillate at a much lower frequency, but 25000uF is large enough to keep the DCbus voltage even for a millisec (depends on the load current), so if you can program a double pulse test on your controller instead of driving the load for a longer time, that would significantly limit the voltage sag.

zombiess

10 MW

peters said:try to change it to 1-1.5us with a 50-100ohm turn-on resistor, and keep the 10nF Cgs also at the FET. But it increases the current transition time and the switching loss.

I've been told that high value gate resistors aren't the greatest idea. I think this was discussed in more detail way back in my very first controller build at some point.

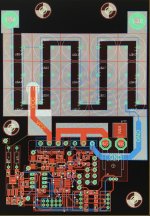

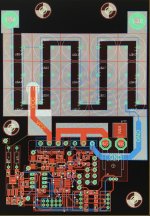

bdj, would you post some pictures of your gate driver design. I'd like to see what you are working with, how the ground planes are laid out, etc. Using short twisted leads to make the connections should not be an issue. I've done it many times myself and at much higher current levels without issues.

I just made this video tonight and it shows scope shots of my motor running, it might be of interest to you for some reference. I have another video I need to put together where I show double pulse testing at +100A and how the wave forms behave.

[youtube]LcJCTB-6k2c[/youtube]

Yes my mistake, it is “High side fet turn on” and “High side fet turn off”.peters said:On your "Low side fet turn on" photo (isn't it the high side if the load is between the output and the GND?)

Returned 10nF and increased low side gate resistor form 10R to 30R.

Low side Vds

Added snubber(2R7 and 10nF) to low side fet DS, picture of Vds

Vgs of higf fet turn on

Vgs of high fet turn off

Vds of high fet

Effect high fet switching on low fet Vgs

Concerning cap near DS I have it already its 1uF. I will try bigger value 4.7uF as soon as I get it. I will go detaily through the post you suggested Peter and do also double pulse test.

Zombiess here are schematic and layout. I am awear that need to do a lot concerning layout and like to hear suggestions.For testing in current setup there is only one gate resistor per fet for both turn on and turn off other stuff like turn off transistor, gate pull down resistor and zener diode are not used. Fets are disconnected and caps from dc link are not used. In second picture I started rework, on cirrent setup polygons are only on dc link and common node DS.

Very nice video with lot of details. Can you try a speed step response from slowestzombiess said:I just made this video tonight and it shows scope shots of my motor running, it might be of interest to you for some reference.

speed to highest to be able to simulate high load and measure current and also Vds overshoot? I suppose that would have highest impact on Vds overshoot?

zombiess

10 MW

bdj, where are you located? You gate driver layout looks like it is lacking good ground planes. Having test points on a gate driver is also something I was taught to avoid as they increase the chances of picking up noise. Gate drivers are one of the most difficult pieces to get correct as they are very noise sensitive and look quite simple on schematics.

I could provide you with a PCB for a stand alone gate driver I designed around the TD350E if you are interested in building it up. Depending on your location and shipping cost, I could send you one of my built stand alone drivers for testing so you could see if the issue is on the gate driver side or power pass side.

I could provide you with a PCB for a stand alone gate driver I designed around the TD350E if you are interested in building it up. Depending on your location and shipping cost, I could send you one of my built stand alone drivers for testing so you could see if the issue is on the gate driver side or power pass side.

zombiess

10 MW

bdj said:Very nice video with lot of details. Can you try a speed step response from slowest

speed to highest to be able to simulate high load and measure current and also Vds overshoot? I suppose that would have highest impact on Vds overshoot?

I'm not quite sure what you are asking for. In the video I go from 0 to full throttle and pull about 40A peak phase current, but I'm not sure if I captured that in the scope shots. I have another video I'm putting together in which I show double pulse testing which will probably be more informative for you.

I looked again video. I am wondering is throttle implemented as slider so when you are giving speed reference you slide fast with your mouse and give speed reference? If so speed reference would have shape of a ramp signal. But for exapmle if you set some lower speed reference first and then just click it on some higher value on slider that would look like speed step reference and current would rise almost instantly. Maybe then it could be more convenient to capture Vds.

Yes thank you for the offer, I would like to try driver. I am in Serbia. For the components I can get them in a two -three weeks because of customs here is very slow. But if possible concering time/costs for me is better to buy complete assembled board from you.

Yes thank you for the offer, I would like to try driver. I am in Serbia. For the components I can get them in a two -three weeks because of customs here is very slow. But if possible concering time/costs for me is better to buy complete assembled board from you.

I think your waveforms are good, I don't see anything unusual, just need a smaller turn-off resistor for higher current.

Maybe a smaller snubber R and C if you want to keep them and want to dissipate less.

The bumps and dips on the low side Vgs are normal, they are partly the Cdg vs. Cgs capacitive voltage division at rising and falling Vds, and partly the voltage on the source inductance during the current transitions. People usually think of only the capacitive division, but the voltage on Ls can also be several volts. The hard thing is to identify the internal gate-source voltage waveform on the silicon chip, because only the external Vgs can be measured:

Vgs_ext = Vgs_int + Ls*dI/dt, and the second term is either positive or negative depending on the direction of the current change. Ls*dI/dt also charge and discharge the internal Cgs through the gate pull-down impedance, either a resistor or a short or an external Cgs. So it is complicated, but with normal gate turn-off resistors (~10..15 ohm or less) I didn't experience any shoot-through. The bump after the reverse recovery needs attention, because then the Vds of that FET is high and Vgs is positive; I think it is on your first picture after "Effect high fet switching on low fet Vgs".

The bumps and dips are also on the high side Vgs, just not always seen separately from the rising and falling edges, and may be filtered out by the external Cgs, if used. The turn-off overshoot after the high side Vds rising edge is the same, but there the L is the total loop inductance minus the Ls of the same FET.

Maybe a smaller snubber R and C if you want to keep them and want to dissipate less.

The bumps and dips on the low side Vgs are normal, they are partly the Cdg vs. Cgs capacitive voltage division at rising and falling Vds, and partly the voltage on the source inductance during the current transitions. People usually think of only the capacitive division, but the voltage on Ls can also be several volts. The hard thing is to identify the internal gate-source voltage waveform on the silicon chip, because only the external Vgs can be measured:

Vgs_ext = Vgs_int + Ls*dI/dt, and the second term is either positive or negative depending on the direction of the current change. Ls*dI/dt also charge and discharge the internal Cgs through the gate pull-down impedance, either a resistor or a short or an external Cgs. So it is complicated, but with normal gate turn-off resistors (~10..15 ohm or less) I didn't experience any shoot-through. The bump after the reverse recovery needs attention, because then the Vds of that FET is high and Vgs is positive; I think it is on your first picture after "Effect high fet switching on low fet Vgs".

The bumps and dips are also on the high side Vgs, just not always seen separately from the rising and falling edges, and may be filtered out by the external Cgs, if used. The turn-off overshoot after the high side Vds rising edge is the same, but there the L is the total loop inductance minus the Ls of the same FET.

Yes I also found docs only about capacitive dividers and influence of change of Vds on Vgs. You are afraid that this bump can be larger and turn on a fet and couse both conduct at same time? This bump was even higher when did not applied external Cgs. Maybe it will be little less by applying GS pull down resistor? In any way I have to do proper layout for gate driver. I read here on some posts about choosing dead time, what would be right procedure? To wait until full Vgs rise would be to much?

Yes, when both FETs conduct that is shoot-through or cross-conduction, but I never had that.

By default I set the dead time to 1us and have the Vgs fully turned off (from 100% to close to 0V) within that with the turn-off resistor. The other side FET Vgs starts to rise after that 1us, and there is a few 100ns margin until it starts to conduct.

Some gate driver chips have Miller-clamp, that is a low impedance pull-down that helps to keep the Vgs low, but it's not always needed.

By default I set the dead time to 1us and have the Vgs fully turned off (from 100% to close to 0V) within that with the turn-off resistor. The other side FET Vgs starts to rise after that 1us, and there is a few 100ns margin until it starts to conduct.

Some gate driver chips have Miller-clamp, that is a low impedance pull-down that helps to keep the Vgs low, but it's not always needed.

zombiess

10 MW

I'll second Peters recommendation for 1000ns dead time as a starting point and that the waveforms are good enough. They will never be picture perfect. Just be aware that as you go up in current, the layout becomes MUCH more critical to success.

My TDE350 gate driver design requires 800ns to ensure enough safety margin over the full temp range. The basic rule is to not have dead time exceed 5% of your switching period. 1us of DT puts you at a max of 20us period / 50kHz PWM to stay within that rule. The reason to stay under 5% is to minimize dead time distortion. Deadtime must be calculated from spec sheet max and min on off times. I've posted an example in my 18FET design and there are comments made by highhopes in there. Highhopes advice is solid if you search his posts. He has done power electronics for aerospace. I've had great success following his advice. For now I'd just go to 1us and then research how to calculate it. I'll look through my notes for an example to share with you.

I am not a fan of gate drivers without an active Miller clamp for anything that will switch high currents. Miller effect turn on will ruin your day and possibly your power stages day as well.

How much current do you plan to push?

My TDE350 gate driver design requires 800ns to ensure enough safety margin over the full temp range. The basic rule is to not have dead time exceed 5% of your switching period. 1us of DT puts you at a max of 20us period / 50kHz PWM to stay within that rule. The reason to stay under 5% is to minimize dead time distortion. Deadtime must be calculated from spec sheet max and min on off times. I've posted an example in my 18FET design and there are comments made by highhopes in there. Highhopes advice is solid if you search his posts. He has done power electronics for aerospace. I've had great success following his advice. For now I'd just go to 1us and then research how to calculate it. I'll look through my notes for an example to share with you.

I am not a fan of gate drivers without an active Miller clamp for anything that will switch high currents. Miller effect turn on will ruin your day and possibly your power stages day as well.

How much current do you plan to push?

I will find the info about dead time calculation. I see from datasheet of TD350E that miller clamp can be used in configuration to short G-S when fet is turned off. In reality are there any spikes, bumps, disturbances.. on Vgs voltage or it really looks like flat line near zero V?

Maximum current I am aiming is 30-40A and 100V dc max supply. It will be H bridge for brushed DC motor which has high inductance about ~2mH so I could go also with lower pwm frequency.

Maximum current I am aiming is 30-40A and 100V dc max supply. It will be H bridge for brushed DC motor which has high inductance about ~2mH so I could go also with lower pwm frequency.

zombiess

10 MW

bdj said:I see from datasheet of TD350E that miller clamp can be used in configuration to short G-S when fet is turned off. In reality are there any spikes, bumps, disturbances.. on Vgs voltage or it really looks like flat line near zero V?

The amount of induced voltage on the gate trace is dependent on how well your gate driver is laid out. Improper trace routing and large loop area can certainly induce turn on. The lower the Vgs(th) of a MOSFET, the more likely this is to happen. I have done tests with and without the Miller clamp and it certainly makes an improvement.

For more info on dead time setup, check out this post:

https://endless-sphere.com/forums/viewtopic.php?f=30&t=51342&p=874347&hilit=deadtime+zombiess#p874347

More info on the Miller clamp:

https://endless-sphere.com/forums/viewtopic.php?f=30&t=51342&p=875302&hilit=miller+clamp+zombiess#p875302

Peters I read a post from

Zombiess I read posts you suggested. Concerning the dead time explanation with counting for propagation times and delays through the nodes and connections, this is math approach concerning data from datasheets, but for first steps will it be also valid by looking at scope Vgs from hi and low fets at same time and determine “good” deadtime? If I understood good from some other posts here fet can be considered off( with some low current) as soon as Vgs falls under its treshold value ? And also fet can be considered on(with some low current) as soon as Vgs reaches treshold value? So regarding this scenario can deadtime be modified so we would have some small part of “overlapping” form Vgs of both high and low fet? And current through both fets would be small.

Can you explain me what is meant by high low frequency distortion if dead time is more than 5% of switching period? Does it mean that phase currents would have a lot of harmonics and ripple in compare to true sine wave because we don’t have controll over it for a amount of dead time?

Concerinig transconductance work of mosfet that is reffering to linear mode? Short pulses can place fet in this mode. Concerning bootstrap gate drivers they also requre minimum pulse width to be able to properly charge bootstrap cap. So depending on charge current and cap size bootstrap gate driver can put higher demand for minimum pulse width. I read also in some post that minimum pulse width can be issue for low speed operation. Why this could be issue? Wouldn’t speed loop controller be able to “fight” against this scenario with its positive and negative output and also handle low speed operation something like hysteresis controll ?

and lot of tips for gate driver and power stage layout desing. But the thing I am missing is gate driver ground. I plan tu put gate driver and power stage on same board. Is it good practice to route connections on top and bottom layer (plan is to go with 2 layer board) and place ground on top layer and make connection of gate driver ground with power stage ground only in one point this point is lower fet S ? High current traces will not overlap with gate driver traces. For power stage plan is to have minimal surface with maximum overlap between dc bus + and dc bus -. Common node D-S as short as possible and nothig abowe or below.peters said:Shaman's older board had a very similar ringing at low voltage:

viewtopic.php?f=7&t=97699&start=125#p1445800

Zombiess I read posts you suggested. Concerning the dead time explanation with counting for propagation times and delays through the nodes and connections, this is math approach concerning data from datasheets, but for first steps will it be also valid by looking at scope Vgs from hi and low fets at same time and determine “good” deadtime? If I understood good from some other posts here fet can be considered off( with some low current) as soon as Vgs falls under its treshold value ? And also fet can be considered on(with some low current) as soon as Vgs reaches treshold value? So regarding this scenario can deadtime be modified so we would have some small part of “overlapping” form Vgs of both high and low fet? And current through both fets would be small.

Can you explain me what is meant by high low frequency distortion if dead time is more than 5% of switching period? Does it mean that phase currents would have a lot of harmonics and ripple in compare to true sine wave because we don’t have controll over it for a amount of dead time?

Concerinig transconductance work of mosfet that is reffering to linear mode? Short pulses can place fet in this mode. Concerning bootstrap gate drivers they also requre minimum pulse width to be able to properly charge bootstrap cap. So depending on charge current and cap size bootstrap gate driver can put higher demand for minimum pulse width. I read also in some post that minimum pulse width can be issue for low speed operation. Why this could be issue? Wouldn’t speed loop controller be able to “fight” against this scenario with its positive and negative output and also handle low speed operation something like hysteresis controll ?

I reckon Zombiess's new design is the best practice for gate driver connection, because the gate circuit junction on the FET legs is as close as possible to the case, that produces the smallest bumps and dips we talked above (otherwise 2-3V bigger spikes can be induced on a 3-5mm long S pin at high current at fast switching that is not easy to handle and may kill the gate driver chip), and also perpendicular to the power signals, so there is no induced voltage in the driver loop.

But if you want to place them on the same board (with dual high+low driver chips I suppose), then try to fully separate the gate driver circuit from the power stage, they shouldn't be overlapped.

"make connection of gate driver ground with power stage ground only in one point this point is lower fet S ?" - Yes, but he thing is there are three S pins, each with their own spikes, so if the gate drivers are not isolated, then a common low impedance GND plane is needed for the 3 drivers, and maybe small serial resistors on the gate driver connection to the S pins, that prevents high currents from passing on the driver GND plane.

"Common node D-S as short as possible and nothig abowe or below." - I have a different opinion, because that node is a part of the output loop in series with the 2 FETs, the DCbus and the closest capacitor (closest by impedance, not by distance), and a goal is to minimize that inductance, so I overlap the common D-S node with either DCbus+ or -.

But if you want to place them on the same board (with dual high+low driver chips I suppose), then try to fully separate the gate driver circuit from the power stage, they shouldn't be overlapped.

"make connection of gate driver ground with power stage ground only in one point this point is lower fet S ?" - Yes, but he thing is there are three S pins, each with their own spikes, so if the gate drivers are not isolated, then a common low impedance GND plane is needed for the 3 drivers, and maybe small serial resistors on the gate driver connection to the S pins, that prevents high currents from passing on the driver GND plane.

"Common node D-S as short as possible and nothig abowe or below." - I have a different opinion, because that node is a part of the output loop in series with the 2 FETs, the DCbus and the closest capacitor (closest by impedance, not by distance), and a goal is to minimize that inductance, so I overlap the common D-S node with either DCbus+ or -.

zombiess

10 MW

bdj said:Zombiess I read posts you suggested. Concerning the dead time explanation with counting for propagation times and delays through the nodes and connections, this is math approach concerning data from datasheets, but for first steps will it be also valid by looking at scope Vgs from hi and low fets at same time and determine “good” deadtime?

Not unless you are able to simulate all operating conditions. Stick to the math approach, it's easy and safe. I learned from Highhopes, he did this kind of work in the aerospace realm and that's what he taught to me, so I stick to it. The design approach I was taught by him is pretty much setup to work every time. I only deviate from it when I have good reason and a solid understanding of what I'm doing that I can justify. A dead time of 1us will support 50kHz and still be 5% of the period. If you want to succeed in designing a motor drive which is functional and doesn't suffer random failures, you need to be conservative.

If I understood good from some other posts here fet can be considered off( with some low current) as soon as Vgs falls under its treshold value ? And also fet can be considered on(with some low current) as soon as Vgs reaches treshold value? So regarding this scenario can deadtime be modified so we would have some small part of “overlapping” form Vgs of both high and low fet? And current through both fets would be small.

Yes it's possible to have a small overlap. There is a technique where a small amount of shoot through is purposely induced in order to reduce overshoot. Bad idea unless you REALLY know what you are getting into and have developed a specialized controller for this purpose.

Can you explain me what is meant by high low frequency distortion if dead time is more than 5% of switching period? Does it mean that phase currents would have a lot of harmonics and ripple in compare to true sine wave because we don’t have controll over it for a amount of dead time?

Excessive dead time will cause an introduction of low frequency harmonics which will increase THD. Increased THD = additional motor heating and reduced torque. In aerospace they have rules about production of LF harmonics. These harmonics start to become excessive > 5% dead time, I've played around with this in simulation and measured THD. Can you exceed 5% in your application without issue, sure, but you'll need to switch > 50kHz with 1us dead time. Even my slow TD350E gate driver runs at 800ns so it's capable of > 50kHz. Most motors do not require such a high switching frequency. The required switching freq is dependent on motor inductance. The motor inductance and switching freq also dictate the amount of DC link cap required to handle the ripple current.

Concerinig transconductance work of mosfet that is reffering to linear mode? Short pulses can place fet in this mode. Concerning bootstrap gate drivers they also requre minimum pulse width to be able to properly charge bootstrap cap. So depending on charge current and cap size bootstrap gate driver can put higher demand for minimum pulse width. I read also in some post that minimum pulse width can be issue for low speed operation. Why this could be issue? Wouldn’t speed loop controller be able to “fight” against this scenario with its positive and negative output and also handle low speed operation something like hysteresis controll ?

Yes, short pulses can cause a partial turn on. That is why the motor controllers have a minimum pulse width setting.

Low speed operation could also depend on the load. A motor running at low speed and no/low load will only require short pulse widths due to the low current demand.

There are different types of controller configs. Some are PI, some PID, speed control, current control, speed-current control which is usually 2 cascaded PI controllers with a inner PI control loop managing current running about 10x faster than an slower outer loop voltage controller whose output is fed into the inner PI controllers set point. A lot of this stuff won't make sense unless you start simulating it and playing around, or you happen to be a control systems engineer.

Similar threads

- Replies

- 5

- Views

- 3,043

- Replies

- 24

- Views

- 3,051

- Replies

- 22

- Views

- 13,220

- Replies

- 19

- Views

- 5,682