Futterama said:

zombiess said:

Does that mean no more help from you?

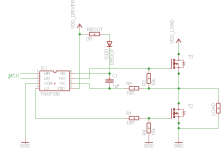

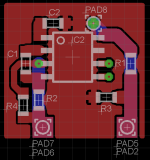

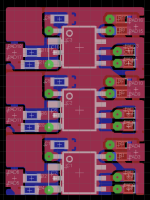

I can't help you with concepts I am unfamiliar with. Right now I know one method of design that has been proven to work. I am not knowledgeable enough to help beyond fundemental basics, and even that is pushing my skill level. I am still a noob to most of this and only have a single 90% proven design. I had a ton of help from highhopes but I understand what he taught me... well almost all of it. I got somewhat lucky by having my very first ever design work as planned. I am told 2 to 3 designs are usually required. I am of course most familiar with the td350e driver and have figured out most combo drivers are a pain to properly layout without doing a 4 layer board, but yours doesn't look so bad to layout. I can see why as i am now working on number 2 which is even better than what i posted, much smaller too. Laying out the board is the hardest part since its always going to be some compromise, but certain rules should be followed. If you download and steady the layout I did you can see how I did the ground planes for high and low side. Since you are paralleling the gets you should put a small gate resistor on each. The value should be about an order of magnitude lower than the main gate resistor.

Some suggestions.

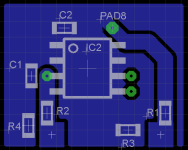

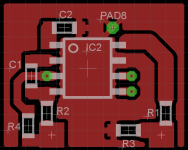

Make 2 ground planes, both on the bottom with a gap between them. One gets connected to high side source, the other to low side source.

Keep all components smd in the gate driver and placed on the top layer using as few bias and traces to the bottom side as possible. This takes many attempts usually, I spent several hours a day for a week due to how many components are in my driver.

Size your boot strap cap appropriately, there are online calculators but my guess is 6 to 10uF xr7 will be good.

Add a 10uF xr7 cap to the 15v rail, it should be very close to the driver, right after it use a 0.1uF bypass cap. Order should be power, 0.1uF, 10uF, driver ic. I skimmed the datasheet of your driver and they show this same configuration.

If fairchild offers a demo board for this chip, get the board layout or buy one. All the hard design work is done for you and you can borrow it

I went the hard route because I wanted to learn all the details and the math... I am a sick bastard like that, I don't accept just because usually always want to know why.

If I have some time... which I don't right now I will try to do a quick and dirty layout with your driver if so you can see some of the concepts. The other guys on here can then help tear apathy any mistakes I made.