Futterama

1 kW

Location filled, I thought it was enough to put in my country, but that obviously didn't show up as I thought.

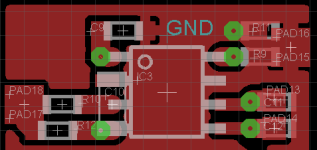

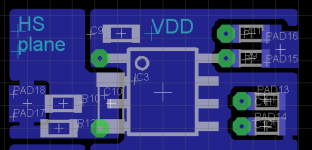

zombiess, R10 at pin 3 of the IC is the high side output gate drive, that's on the top layer where I also have my GND plane. Below R10, R12 and a part of the GND plane, I have the HS plane, HS is high side source. The HS plane is overlapping the GND plane, is that a bad idea? After you mentioned the noise issue, I can see that the HS plane should probably not be bigger than the high current path for the gate, on the top side.

zombiess, R10 at pin 3 of the IC is the high side output gate drive, that's on the top layer where I also have my GND plane. Below R10, R12 and a part of the GND plane, I have the HS plane, HS is high side source. The HS plane is overlapping the GND plane, is that a bad idea? After you mentioned the noise issue, I can see that the HS plane should probably not be bigger than the high current path for the gate, on the top side.