Here is some additional testing that I performed today. It's not too exciting, but it does demonstrate how important it is to understand your test equipment and it's limitations. Common Mode noise picked up by the probe leads can make you think there is an issue where one does not exist. I figured I'd have a difficult time making measurements with high current pulse tests due to the coil radiating EM like a weapon, so I took some time to try and study it.

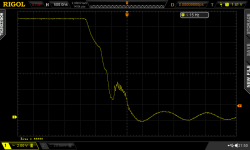

This is the common mode noise reading of a regular probe (yellow) and a differential probe all connected to the exact same spot to measure the common mode noise from the 5uH coil. Air coils radiate wildly.

This is showing the CM at 650A from a 64v supply. As can be seen, even the differential probe lead is picking up a good amount of CM. After taking this reading, the scope was set with each input to ground while the pulses were conducting to verify that it is indeed CM noise and not real noise being picked up on the driver circuit. That test passed 100% with zero visiable noise even at the most sensitive scales. As can be seen, the differential has slightly less CM in the sine signal (400mV scale vs 500mV scale) and throughout the rest of the trace the switching noise form a nearby SMPS is not visible, it is fully rejected as is expected from this type of probe.

Probe used is a Tektronix P6045 with amplifier and no 10x reducer. Setup procedure was completed and the warm up time of 30 mins allowed for everything to settle. The blue trace is the differential probe on channel 2 in 1x mode set for 200mV per division, scope configured for a 2x probe to make voltage readings accurate. Scope was configured for 20Mhz bandwidth limiting and normal capture. Connection was made with a 50 ohm cable running to a 50 ohm terminator since the scope, a Rigol DS2072 only has 1M inputs. For future readings any time this signal appears it has to be noted as not real and due to CM picked up by the measurement instrumentation.

This test was done at 650A with all probes shorted and connected to the high side MOSFET source. High side was powered on but held low to make sure the miller clamp was active.

Measurement of the G-S pins of the high side MOSFET (non switched, only low side was switched in this testing) showing a

Zoomed in view of the G-S signal using the differential probe on the high side MOSFET (blue trace). Yellow trace shows the CMRR picked up by the passive probe when connected to the high side source. Removing the probe connection has no effect on the blue trace of channel B. Small pulses on yellow trace show switching noise from a nearby SMPS buck converter.

400a at 31v, 740mV of CMRR is present.

Reality of the noise is 740mV - 672mV of CM = ~68mV of noise on the high side G-S

This shows the full 200uS pulse width discharging, yellow trace is still measuring probe/lead CM. The same 740mV spike from the above picture is still visible, but it is only common mode noise and not actually present on the gate driver.

Same as above initial test, but the current has now been increased to 650A at 64v. As can be seen the CM is now 1.256V. If this was real there is a significant concern that a MOSFET might be turned on due to miller effect which would lead to a shoot through event.

This test shows more induced Voltage D-S. The real G-S noise being picked up by the opposite gate driver is 1.256 - 672 = 584mV on the G-S with a 650A pulse

View attachment 3

650A, 64v test for 200uS. CMRR needs to be removed to find the real noise level on the G-S of the other sides inverter. The true turn on peak was not located, but the CMRR on a 650A pulse is 1.256v. This leads me to believe the only miller effect voltage being generated is maybe in the 100mV range which is significantly below the VGSth spec of the IRFP4568 MOSFET which is 3.0V.

Testing of the digital side as also done to look for noise. Only the common mode noise was visible. The common mode noise nicely shows the delay between the digital signal and the actual switch event at the MOSFET. Channel had it's probe lead and tip shorted on the high side source. Ground clip from differential probe went to this same location to keep ground references the same. The digital output was then measured using the differential probe with a 100X adaptor on it. As een below, the digital input is a 4.4 signal to the optocoupler. The ringing noise denotes the D-S switch of the MOSFET bank under test, this is not real on the digital side.

Zoomed in view of the propagation delay caused by the gate driver circuit. This demonstrates the digital signal being issued and then no output on the D-S happening for 1.32uS which is the amount of propagation delay in the gate driver. Yellow trace is once again measuring CM.

Preliminary Thoughts:

Preliminary Thoughts:

The experimental layout of 2 parallel buss bars run down the center vs a laminated setup, using internal shielding of the opposite bus polarity on an inner layer appears to significantly reduce the noise picked up by the gate drivers during high current. Common mode noise is a major issue when measuring as one has to filter out false noise from real noise. The above pictures shows +8v of noise on the digital side which does not really exist on the output of the pulse generate. This is all noise picked up In the scope leads.

Shoot through protection happens in ~4.7 uS which has been saving the MOSFETs while I torture test them. I have seen spikes as high as 5kA during direct short circuit testing while verifying desat works as expected (5.1 zener allowed current to go much too high). It did not initially due to using a 5.1v Zener Diode. The 6 of these were later exchanged for 5.6v zeners which reduced the trip current from 1.2kA to a more reasonable 725A at 25C. Target goal is 300A phase, but I would like to push this harder and try for 350-400A for short bursts such as dead stop accleration.

During all testing so far the inverter is looking to have very clean signals. I have developed an even better way to create a true laminated bus bar for the power feed which is something this design lacks, but instead has an alternative approach that still allows for the cancelation of large transients on the bus.

At this point I am going to consider my bench testing complete and move on to finishing up the wiring required to hook this up and have it work with a given brain board. In this case it will be Lebowskis chip. Pending success of this controller, I will scale up to more MOSFETs in parallel to continue testing high current controllers.

If this controller success under testing conditions, I will considering moving up to try very high currents for a controller along with improvements to the layout for minimizing noise.